一種基于FPGA的復數浮點協方差矩陣實現

1.4 浮點復數乘累加器

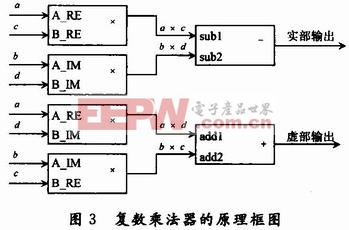

1.4.1 復數乘法器

假設有兩個復數分別為a+jb和c+jd,這兩個數的乘積為:

![]()

復數乘法器的工作原理如圖3所示,其中所用到的加法、減法和乘法器都是基于浮點的運算。值得一提的是,在實現浮點加減法的時候,可以將尾數連同符號位轉化為變形補碼形式后再進行加減運算。這樣做的目的是方便判斷數據是否溢出(變形補碼判斷溢出的規則是:當兩位符號位不同時表示溢出,否則無溢出。無論數據是否溢出,第一位符號位永遠代表真正的符號),若溢出,則將尾數右歸,指數部分加1,若沒有溢出,則將尾數左歸(規格化)。浮點乘法相對較簡單,對應階碼相加,尾數相乘可以采用定點小數的任何一種乘法運算來完成,只是在限定只取一倍字長時,乘積的若干低位將會丟失,引入誤差。

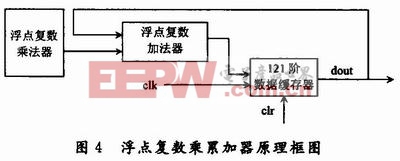

1.4.2 浮點復數乘累加器

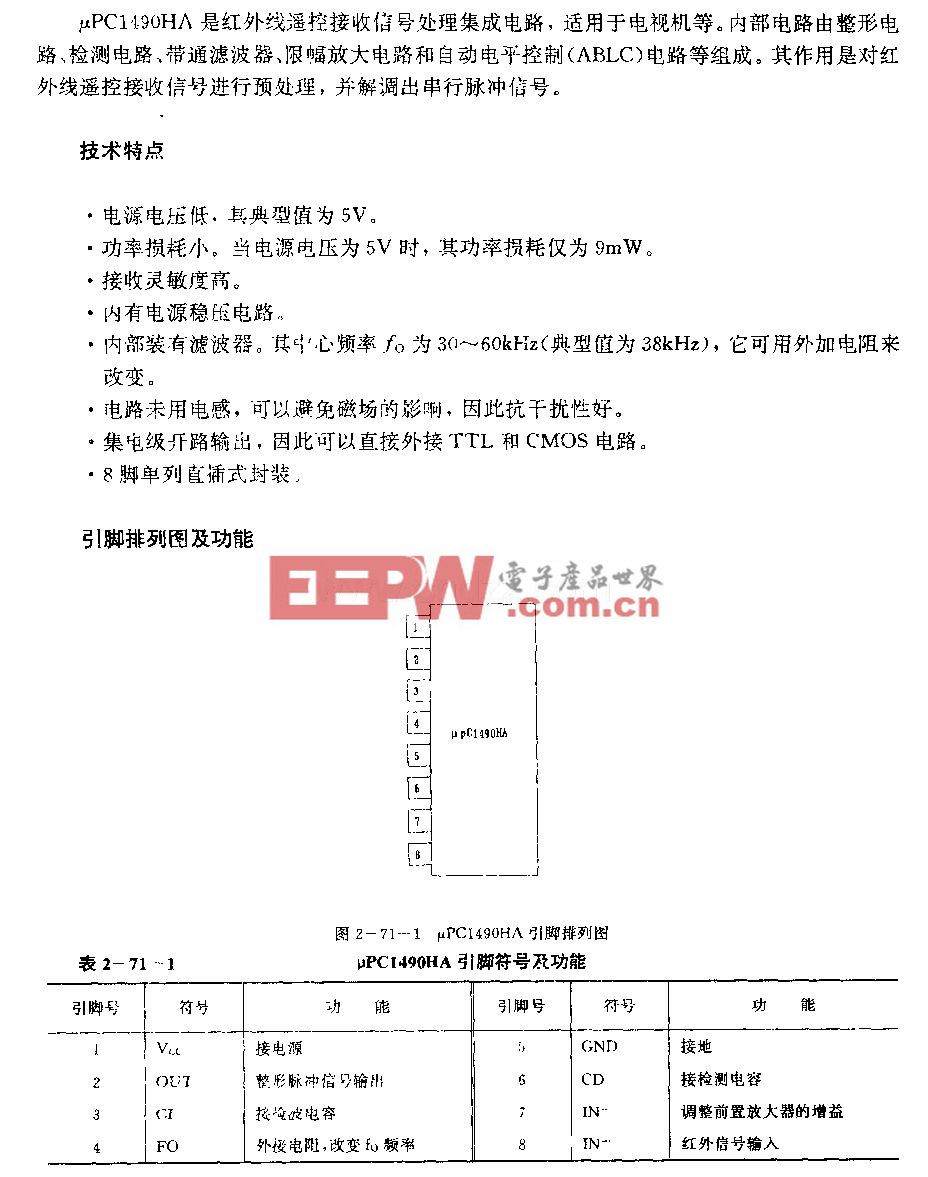

以11個陣元的圓陣為例,實現串行處理方案的浮點復數乘累加器的原理如圖4所示,實部和虛部(雙通道)的乘累加器模塊工作原理一樣。

121階數據緩存器實際上就是121個數據鎖存器級聯形成的一個移位寄存器,初始狀態為零。當浮點復數乘法器有輸出的時候,啟動數據緩存器與之進行加法操作,121個時鐘周期以后可以實現一次快拍采樣的矩陣累加。累加清零信號由時序控制器給出,當所有的快拍采樣點運算都結束之后,數據緩存器輸出累加結果(即協方差矩陣的運算結果),同時控制器送出一個清零信號,清零121階數據緩存器。

評論