一種基于FPGA的RFID無線通信系統的實現

1.3.2 SPI硬件設計

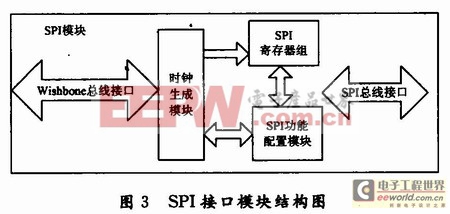

圖3是本文無線通信系統中SPI模塊的結構圖,該系統中的SPI主要由時鐘生成模塊,SPI寄存器組,SPI功能配置的模塊組成,并且通過Wishbone總線與控制器相連,具體設計如下:

時鐘生成模塊:由于SPI模塊是基于FPGA來實現的,而FPGA外部提供的時鐘較快(50 MHz或100 MHz),不適合與NRF905的SPI接口進行通信(1 Hz~10 MHz),所以需要分頻來使時鐘慢下來。但是至于幾分頻是由SPI功能配置模塊來完成的。其次由于SPI協議指出數據可在上升沿或下降沿觸發,所以還需要對時鐘的上升沿或下降沿進行鑒別(也稱抓沿程序),這個功能也由這個模塊完成。

SPI寄存器模塊:這個模塊實現的是一個由16個8位寄存器組成的128位的寄存器組,也就是說通過SPI接口一次性可收發8~128位的串行數據。具體操作由SPI功能配置模塊來完成。

SPI功能配置模塊:這個模塊相當于一個SPI控制器,通過對其寄存器的配置來決定時鐘的分頻數,收發數據位數,時鐘上升沿或下降沿傳輸數據等,而對這些寄存器的配置是由控制模塊完成的。下面就配置寄存器做一些簡要說明。

首先介紹控制寄存器:

- 控制寄存器第O位go:是否開始發送。

- 控制寄存器第1位rx_negedge:接收數據是下降沿還是上升沿。

- 控制寄存器第2位tx_negedge:發送數據是下降沿還是上升沿。

- 控制寄存器第3~9位char_len:發送數據的位數(因為SPI是全雙工的,所以這實際上也是接收數據的位數)。

- 控制寄存器第10位lsb:是從高位發送還是地位發送。

- 控制寄存器第11位ie:讀寫完成之后是否發送中斷信號。

- 控制寄存器第12位ass:是否自動產生片選信號。

- 分頻寄存器:spi_divider_sel。

- 狀態寄存器:spi_ctrl_sel。

- 數據寄存器O:spi_tx_sel[0]。

- 數據寄存器1:spi_tx_sel[1]。

- 數據寄存器2:spi_tx_sel[2]。

- 數據寄存器3:spi_tx_sel[3]。

- 片選信號寄存器:spi_ss_sel。

評論