一種基于FPGA的誘發電位儀系統研究與設計

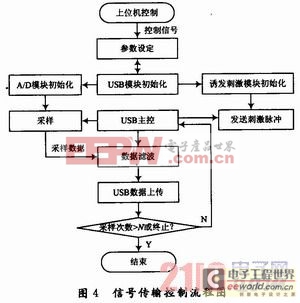

2.4 信號傳輸控制模塊

在FPGA內部將完成誘發電位儀同步信號發生模塊、A/D轉換器的控制、USB傳輸控制端口和上位機命令解析模塊,從而形成一整個誘發電位儀核心處理控制模塊,可以方便地使用各個模塊來完成外圍器件的初始化、工作模式配置和系統的數據傳輸。圖4為信號傳輸控制流程圖。

2.5 數字信號處理模塊

數字信號處理模塊集成到FPGA中,可以將算法拆分,形成大規模的數字信號處理并行結構,將極大地提高處理速度,且性能不會下降,如模式識別算法、盲源分離算法等,均比較適合集成到FPGA中實現。在前置模擬電路放大之前,腦電信號為微弱混雜的信號,需要做一些濾波處理,而此處可以將前段部分的帶通濾波電路轉化為數字濾波器,設置到FPGA芯片中去,可簡化電路結構,使系統整體體積大大減小。本設計在FPGA芯片中搭建了四階無限脈沖數字濾波器,其系統傳遞函數H(z)如下:

將誘發電位信號放大模/數轉換之后的數據實時經過濾波,實現信號的前置處理,經測試效果良好。利用FPGA的并行性,在每個通道設置一個數字濾波器,大大增強了系統實時性,而且可探索自適應、小波數字濾波器等設計,在硬件層次提高系統的處理能力。

3 高精度多通道模/數轉換器ADSl258

在誘發電位儀采集系統中,模/數轉換模塊芯片的選取對整個采集系統的結構和性能影響非常大,本文模/數轉換芯片選用ADSl258器件,使得本系統達到多通道高分辨率的要求。

3.1 ADSl258的主要特點

ADSl258是16通道24位分辨率的低噪聲模/數轉換芯片,全量程5 V的單端輸入范圍或者±2.5 V的真雙極輸入,每個通道采樣速率最高23.7 KSPS(16通道同時采樣),單個通道采樣最高可達400 KSPS,通過SPI兼容接口進行工作模式配置和串行數字通信,使用方便。選用此芯片,電壓分辨率即可達到1 μV,因此信號放大和調理預處理電路的放大倍數只要100倍就可滿足誘發電位儀的技術要求,大大簡化了前級電路。

評論