一種基于FPGA的誘發電位儀系統研究與設計

2 FPGA軟件模塊設計

2.1 FPGA的優勢

FPGA即現場可編程門陣列,是在CPLD的基礎上發展起來的新型高性能可編程邏輯器件,它既繼承了ASIC的大規模、高集成度、高可靠性的優點,又克服了普通ASIC設計周期長、投資大、靈活性差的缺點,逐步成為復雜數字硬件電路設計的理想選擇。不同于傳統的誘發電位儀設計,本文將大部分分立元件實現的功能集成到了FPGA芯片中,實現多種刺激模式和濾波模塊以及實現對外圍器件的控制,不僅提高了集成度使儀器小型化、便攜化成為可能,而且片內模塊可反復修改,提高了設計開發效率降低了成本,也可以方便地實現各模塊之間的同步。

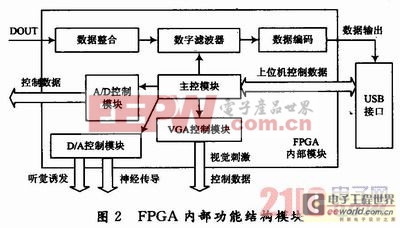

2.2 軟件模塊整體設計

本設計中,FPGA芯片軟件模塊包括了誘發電位刺激模塊、信號傳輸控制模塊和數字信號處理模塊三大部分;由共同的同步信號協同合作,完成誘發電位儀的誘發刺激、信號的傳輸、數字濾波等核心控制處理功能。FPGA內軟件模塊框圖如圖2所示。

2.3 誘發電位刺激模塊

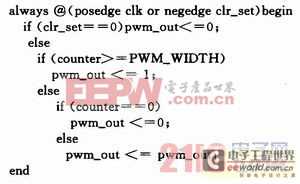

在FPGA芯片中設計了誘發電位刺激模塊,主要功能包括:聽覺誘發電位刺激、神經傳導刺激和視覺誘發電位刺激。刺激信號主要由脈沖信號進行控制,通過 FPGA芯片可以直接輸出脈沖信號和VGA控制信號。聽覺誘發刺激信號和神經傳導刺激信號可由FPGA輸出的脈沖信號經功率放大后產生,在此聽覺誘發電位刺激信號為雙通道,一路信號產生脈沖信號如PWM(脈寬調制)波,另一路由FPGA芯片內部模塊通過DA轉換器產生白噪聲,而神經傳導刺激信號可直接由 FPGA輸出PWM脈沖直接驅動電壓放大器生成。通過Verilog硬件描述語言,在FPGA中實現誘發電位刺激源信號,并通過FPGA端口輸出,例如在芯片中使用以下代碼可產生一個占空比為PWM_WIDTH:1的PWM波形:

視覺誘發刺激信號由在FPGA芯片中存儲的刺激圖像數據直接產生VGA時序控制信號,控制VGA顯示器顯示棋盤格或彩條刺激圖像給予人體視覺刺激。

誘發電位刺激信號主要參數包括刺激脈寬、刺激頻率、刺激強度、刺激類型和刺激模式,USB芯片從上位機接收到參數配置信號,傳遞給誘發刺激信號生成模塊發出脈沖。例如,生成聽覺誘發電位刺激信號如圖3所示,它的刺激脈寬為O.2 ms,刺激頻率為12 Hz,設置某一刺激強度(由分貝進行度量);而生成視覺誘發電位刺激信號,刺激頻率為2 Hz,刺激類型為棋盤格模式,刺激模式為16×16。

評論