verilog中阻塞賦值和非阻塞復制的理解

阻塞和非阻塞語句作為verilog HDL語言的最大難點之一,一直困擾著FPGA設計者,即使是一個頗富經驗的設計工程師,也很容易在這個點上犯下一些不必要的錯誤。阻塞和非阻塞可以說是血脈相連,但是又有著本質的差別。理解不清或運用不當,都往往會導致設計工程達不到預期的效果,而其中的錯誤又很隱晦。下面我給大家談談阻塞和非阻塞語句的本質區別和在FPGA設計中的不同運用。

阻塞語句

顧名思義,即本條語句具有影響下一條語句的作用,在同一個進程always中,一條阻塞賦值語句的執行是立刻影響著下條語句的執行情況和結果。如果該條語句沒有執行完,那么下條語句不可能進入執行狀態的,因此,從字面層上理解,該條語句阻塞了下面語句的執行。阻塞語句最能體現verilog HDL和C語言之間的血緣關系,比如,在時鐘沿觸發的always進程里,若先執行b=c,再執行a=b,那么本質上,在一個時鐘沿觸發里面,a=c成立,即是說,不要b變量,直接在進程里賦值a=c,結果是一樣的。這和c語言中b=c,a=b性質相同。

非阻塞語句

非阻塞語句應該來說,更能體現硬件電路的特點。這正是非阻塞語句廣泛應用于時序邏輯電路的原因。接上面的例子,如果在一個時鐘沿觸發的always進程里面,b=c,a=b那么就不可能直接在進程里面賦值a=c.因為c的值要經過兩個時鐘延遲才傳到a里面,即c若從0變為1,那么要經過兩個clk上升沿才傳到a,a的值才從0變為1。兩次賦值正是體現了兩個時鐘延遲的特點。這種特點即是非阻塞語句非阻塞的的原因導致的,就是說,a=b,不會因為b=c沒有執行完畢而不執行,只要時鐘觸發進程,那么a=b,b=c同時執行。所以,如果c為1,b為0,a為1的話,那么在在非阻塞語句的進程里面,一個時鐘沿到來,由于他們之間是同時執行的,所以把c的1賦給了b,把b的0賦給了a,但是在阻塞語句里面,c的1先給了b,然后b把新賦值的1又給了a,那么a在一個時鐘之后即變成了1。(在一次觸發進程里,無論是阻塞和非阻塞語句,每條語句只能執行一次)

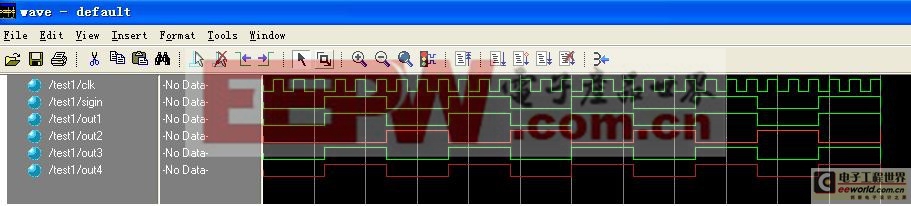

所以從上面的介紹里面,可以看出,阻塞語句是順序執行的,而非阻塞語句是同時執行的,那么,如何在設計里面運用好阻塞語句和非阻塞語句呢,總體上來講,遵循大體原則:阻塞語句運用在組合邏輯電路設計里面,非阻塞語句運用在時序邏輯電路設計里面。但是一般來講,一個設計往往包含著組合邏輯和時序邏輯。可以再細分為以下幾個情況,并可以用阻塞語句和非阻塞語句不同的設計來區別討論它們之間的優缺點,進一步理解清楚。。。。。。(最直觀的說法就是如下仿真一下:觀察out1~out4的變化,就明白了!

`timescale 1ns/100ps

module test1();

reg clk;

reg sigin;

reg out1;

reg out2;

reg out3;

reg out4;

//assign #10 out3 = sigin;

always #10 clk=~clk;

always #70 sigin = ~sigin;

initial

begin

sigin = 1'b0;

clk= 1'b0;

out1 =1'b0;

out2 =1'b0;

end

always @(sigin)

begin

$display('%d',$time);

out1=sigin;

out2= out1;

out3 = sigin;

out4 = out3;

$display('%d',$time);

end

endmodule

#1: 當為時序邏輯建模,使用“非阻塞賦值”。

#2: 當為鎖存器(latch)建模,使用“非阻塞賦值”。

#3: 當用always塊為組合邏輯建模,使用“阻塞賦值”

#4: 當在同一個always塊里面既為組合邏輯又為時序邏輯建模,使用“非阻塞賦值”。

#5: 不要在同一個always塊里面混合使用“阻塞賦值”和“非阻塞賦值”。

#6: 不要在兩個或兩個以上always塊里面對同一個變量進行賦值。

#7: 使用$strobe以顯示已被“非阻塞賦值”的值。

#8: 不要使用#0延遲的賦值。

評論