基于FPGA的SOPC的幾個概念

1、SOC(System On Chip)

a):片上系統,單片上集成系統級、多元化的大功能模塊,構成一個能夠處理各種信息的集成系統 b):集成了許多功能模塊的微處理器核的單芯片電路系統。

c):可以大大縮小系統所占的面積,提高系統的性能和健壯性。

d):已嵌入式系統為核心,集軟硬于一體,并追求最高的集成度,是電子系統設計發展的必然趨勢和最終目標。

e):由硬件和軟件協同完成

2、SOPC(System On a Programmable Chip)

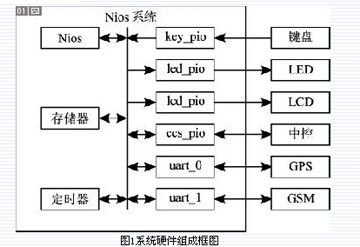

a):片上可編程系統,是Altera公司提出來的一種靈活的,高效的SOC解決方案,它將處理器、存儲器(ROM、RAM等)、總線和總線控制器、IO口、DSP、鎖相環等集成到一片FPGA中。它具有靈活的設計方式,可裁剪,可擴充,可升級,并具備軟硬件在系統可編程功能。

3、IP核 (Intellectual Property核)

a):IP即知識產權,SOC和SOPC在設計上都是以集成電路IP核為基礎,集成電路IP經過預先設計、驗證,符合產業界普遍認同的設計規范和設計標準,并具有相對獨立并可以重復利用的電路模塊或子系統,如CPU、運算器等

b):集成電路IP模塊具有知識含量高、占用芯片面積小、運行速度快、功耗低、可重用性等特點 c):美國Dataquest公司將半導體產業的IP定義為用于ASIC、ASSP和PLD等當中,并且是預先設計好的電路模塊

d):IP核模塊有行為級(Behavior)、結構級(Structure)和物理級(Physical),對應描述功能的不同分為三類:

i.:軟核(Soft IP Core):HDL文本形式提交用戶,經過RTL級設計優化和功能驗證,但其中不含具體的物理信息;也稱虛擬組件(Virtual Compont,VC)

ii.:固核(Fire IP Core );介于軟核和硬核之間,完成門級電路綜合和時序仿真等設計環節,以門級網表的形式提交給用戶

iii.:硬核(Hard IP Core );基于半導體工藝的物理設計,已有固定的拓撲布局和具體工藝,并已經過工藝驗證,具有可保證的性能

評論