基于DSP和CPLD的寬帶信號(hào)源的設(shè)計(jì)

1 引 言

信號(hào)源是雷達(dá)系統(tǒng)的重要組成部分。雷達(dá)系統(tǒng)常常要求信號(hào)源穩(wěn)定、可靠、易于實(shí)現(xiàn)、具有預(yù)失真功能,信號(hào)的產(chǎn)生及信號(hào)參數(shù)的改變簡(jiǎn)單、靈活。本文采用dsp和cpld來設(shè)計(jì)信號(hào)源的控制部分,一方面能利用dsp軟件控制的靈活性,另一方面又能利用cpld硬件上的高速、高集成度和可編程性。使用這種方法可以充分利用軟件支持來生成和加載任意波形數(shù)據(jù),并能方便地實(shí)現(xiàn)對(duì)信號(hào)參數(shù)的控制和對(duì)波形數(shù)據(jù)的隨意修改,同時(shí)又能保證信號(hào)產(chǎn)生的高速、靈活可控。

2 系統(tǒng)結(jié)構(gòu)

采用波形存儲(chǔ)直讀法,即通過對(duì)存儲(chǔ)的波形采樣數(shù)據(jù)進(jìn)行數(shù)模變換,直接生成模擬信號(hào)的一種方法。圖1為信號(hào)源的系統(tǒng)結(jié)構(gòu)。本信號(hào)源可工作于聯(lián)機(jī)和脫機(jī)兩種方式。聯(lián)機(jī)工作時(shí),波形數(shù)據(jù)從微機(jī)加載,由dsp控制,通過cpld內(nèi)的數(shù)據(jù)通道寫入sram,經(jīng)回讀、校驗(yàn)后,從sram內(nèi)高速送入到數(shù)/模轉(zhuǎn)換器件產(chǎn)生雷達(dá)信號(hào)。脫機(jī)工作時(shí),波形數(shù)據(jù)可在系統(tǒng)上電時(shí)由eeprom加載,eeprom中可存放一組波形數(shù)據(jù),也可存儲(chǔ)多組數(shù)據(jù)以方便應(yīng)用。

3 硬件實(shí)現(xiàn)

3.1 tms320f206與eeprom的接口設(shè)計(jì)

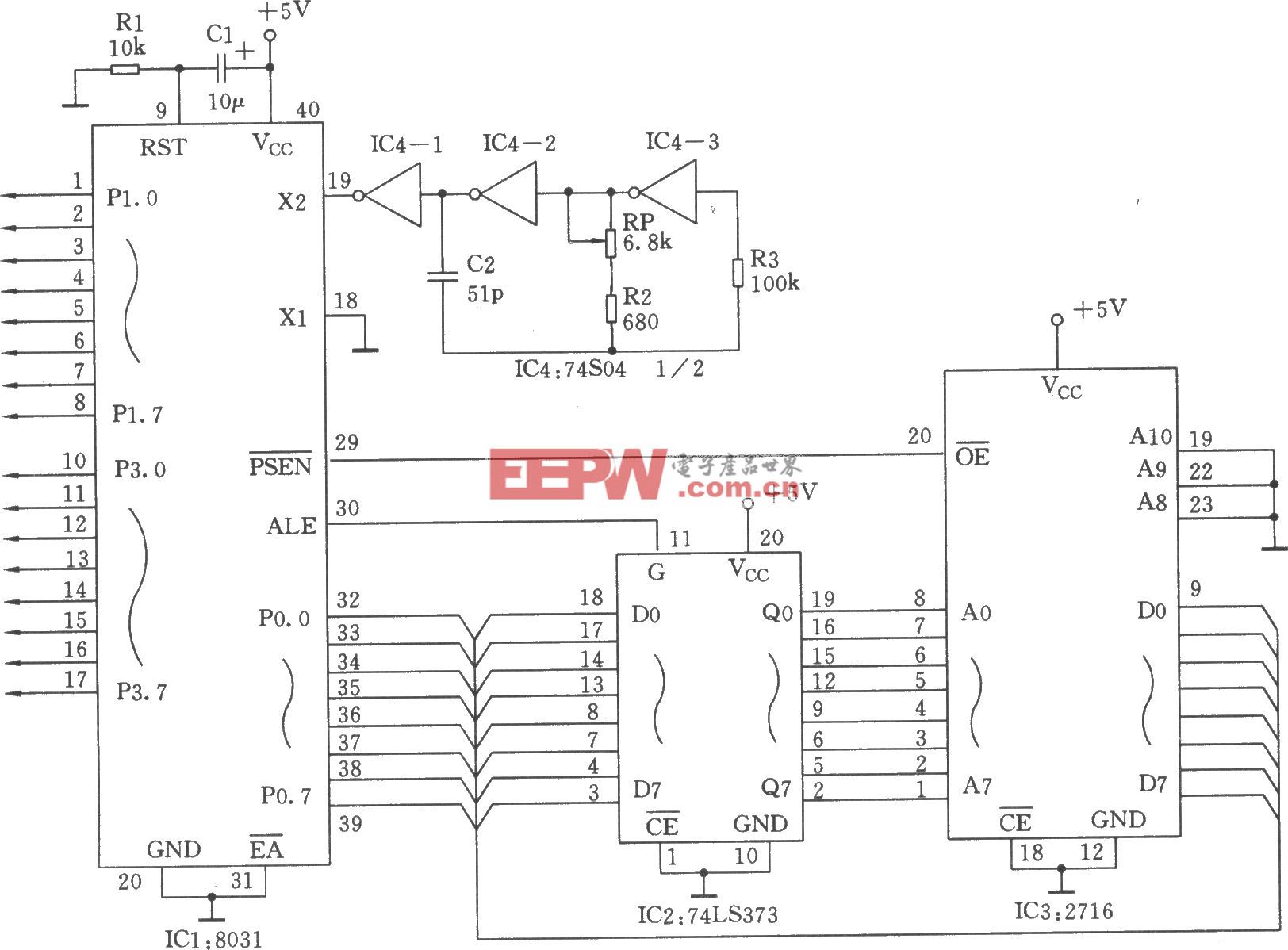

在實(shí)際系統(tǒng)中,dsp采用ti公司的tms320f206芯片,eeprom采用microchip公司的24lc256 cmos串行eeprom(圖2)。tms320f206屬于定點(diǎn)、靜態(tài)cmos數(shù)字信號(hào)處理器。它采用先進(jìn)的哈佛結(jié)構(gòu),具有片內(nèi)外設(shè)、片內(nèi)存儲(chǔ)器及專用的運(yùn)算指令集,這些特點(diǎn)使得此器件使用靈活方便。24lc256工作電壓為2.5v~5.5v,容量為32k×8bit,為兩線串行接口總線,標(biāo)準(zhǔn)與i2ctm兼容。scl為24lc256的時(shí)鐘輸入管腳,sda為其串行地址/數(shù)據(jù)輸入/數(shù)據(jù)輸出管腳。24lc256提供讀順序地址內(nèi)容的操作方式,其內(nèi)部的地址指針在每次讀操作完成之后加1,此地址指針允許在一次讀操作期間,連續(xù)順序地讀出整個(gè)存儲(chǔ)器的內(nèi)容。其時(shí)序如圖3所示。

設(shè)計(jì)中將tms320f206的通用i/o端口io2模擬出scl的時(shí)鐘,io3負(fù)責(zé)將數(shù)據(jù)寫入和從24lc256讀出(tms320f206與24lc256的接口如圖1所示)。脫機(jī)工作時(shí),其流程如圖4。

3.2 cpld設(shè)計(jì)

可編程邏輯器件采用xilinx公司的cpld,型號(hào)為xc95288xl-6tq144c。該器件為144-pin tqfp封裝,內(nèi)部有288個(gè)宏單元,最高工作時(shí)鐘為151mhz。xc95288xl內(nèi)部邏輯分為三部分:tms320f206與微機(jī)接口的通信、高速地址計(jì)數(shù)、sram片選讀寫信號(hào)的產(chǎn)生。

3.2.1 tms320f206經(jīng)過cpld與微機(jī)接口的通信

tms320f206與微機(jī)接口的通信采用并行接口協(xié)議(epp),主要完成從微機(jī)加載數(shù)據(jù)到sram、將數(shù)據(jù)從sram回讀到微機(jī),整個(gè)過程對(duì)于并行接口來說采用查詢方式,對(duì)于tms320f206來說采用中斷方式。tms320f206使用引腳接收由cpld發(fā)出的中斷,通過設(shè)置tms320f206片內(nèi)寄存器irm與icr,使tms320f206響應(yīng)中斷而不響應(yīng)。其時(shí)序如圖5和6所示。

脫機(jī)工作狀態(tài)下,從并口加載數(shù)據(jù)時(shí),微機(jī)將數(shù)據(jù)發(fā)送到并口,并發(fā)出低脈沖,cpld接收stb到后,置busy=1,發(fā)出中斷信號(hào),tms320f206接收到中斷后,控制cpld鎖存數(shù)據(jù),并將數(shù)據(jù)寫入sram,置busy=0;從并口回讀數(shù)據(jù)時(shí),微機(jī)設(shè)置并口為輸入狀態(tài),然后發(fā)出autofeedxt低脈沖,cpld接收到后,置=1,發(fā)出中斷信號(hào)給tms320f206,tms320f206控制cpld從sram讀取數(shù)據(jù)并送到并口,置=0。

3.2.2 高速地址計(jì)數(shù)器設(shè)計(jì)

信號(hào)源中sram在產(chǎn)生雷達(dá)波形時(shí)工作在100mhz的高速時(shí)鐘下,這就要求設(shè)計(jì)的地址計(jì)數(shù)器也工作在100mhz的時(shí)鐘下。在同步計(jì)數(shù)器中,采用超前進(jìn)位(prescalar)技術(shù)來提高其性能,即將前端的、高速計(jì)數(shù)器的超前輸出作為后面的低速計(jì)數(shù)器的計(jì)數(shù)使能。實(shí)現(xiàn)時(shí)我們利用xilinx公司的eda軟件中提供的高效宏單元clbmap優(yōu)化布線,從而使計(jì)數(shù)器內(nèi)部延時(shí)最小。圖7為計(jì)數(shù)器輸出q0~q6的仿真結(jié)果。實(shí)驗(yàn)表明,上述措施對(duì)于提高同步計(jì)數(shù)器的速度

非常有效。

3.2.3 sram片選讀寫信號(hào)的產(chǎn)生

波形存儲(chǔ)單元由兩片高速、低功耗,容量為128k×18bit的靜態(tài)雙口sram構(gòu)成。該器件支持單次讀寫、流水線讀寫、觸發(fā)式讀寫等多種方式,既可對(duì)同一地址單元的高低字節(jié)分別讀寫,也可同時(shí)操作。因此片選讀寫信號(hào)時(shí)序十分復(fù)雜。

本設(shè)計(jì)中sram片選讀寫信號(hào)直接由tms320f206由數(shù)據(jù)線送入到cpld,而不必由cpld內(nèi)部經(jīng)過復(fù)雜的譯碼邏輯電路產(chǎn)生,由此可見dsp+cpld設(shè)計(jì)的簡(jiǎn)單。由于高速讀出波形數(shù)據(jù)送入d/a是在高速時(shí)鐘(100mhz)下進(jìn)行,因此高速讀出時(shí),片選讀信號(hào)一直有效。而在寫入時(shí),由于會(huì)有較長(zhǎng)時(shí)間不對(duì)sram進(jìn)行操作,為避免因時(shí)鐘信號(hào)線上的毛刺而寫入錯(cuò)誤數(shù)據(jù),因此在寫入sram時(shí),片選寫信號(hào)只在寫入的單個(gè)時(shí)鐘周期有效。

4 tms320f206軟件設(shè)計(jì)

信號(hào)源有聯(lián)機(jī)和脫機(jī)兩種工作方式,pcb板上有一個(gè)模式選擇開關(guān),tms320f206通過i/o端口io1檢測(cè)工作模式。tms320f206控制程序首先使tms320f206初始化,設(shè)置各個(gè)片內(nèi)寄存器。然后根據(jù)io1的值決定從eeprom加載還是從微機(jī)加載。程序流程略。

5 實(shí)驗(yàn)結(jié)果

用示波器對(duì)信號(hào)源所產(chǎn)生結(jié)果進(jìn)行測(cè)試,其結(jié)果如圖8和圖9所示,圖8為產(chǎn)生的正弦波和鋸齒波波形,圖9為脫機(jī)模式下產(chǎn)生的線性調(diào)頻信號(hào)的基帶波形,其時(shí)寬為25μs,基帶帶寬為37.5mhz,經(jīng)過4倍頻后,帶寬能達(dá)到300mhz。

實(shí)驗(yàn)結(jié)果表明,運(yùn)用dsp+cpld來設(shè)計(jì)信號(hào)源的控制部分有很大的優(yōu)越性,系統(tǒng)靈活可調(diào)、性能穩(wěn)定,復(fù)雜的控制用軟件實(shí)現(xiàn)簡(jiǎn)單,系統(tǒng)的高速特性也得到滿足。

評(píng)論