三階單環Delta-sigma調制器在ADC中的應用

2.3 Verilog語言行為級建模

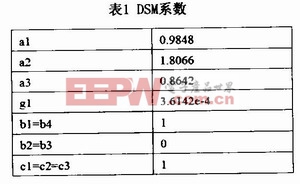

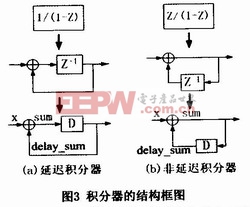

圖2所示的是一種單路差異積分器調制器,可用延遲積分器和非延遲積分器,以及各種前饋和反饋路徑組合而成。在Matlab結構中對應的積分器轉換成Verilog硬件描述框圖的過程如圖3所示

本文使用Verilog硬件語言來實現單回路差異積分調制器,由時鐘控制構成延遲積分器與非延遲積分器的相加動作。assign指令使等式兩邊永遠處于活動狀態,而alwavs指令將會在時鐘正好觸發時將sum的值存入寄存器delay_sum中,因此,所有的積分器將會在每一次時鐘完成時完成一次累加動作。同理,非延遲積分器是由相同的程序代碼組成。實現延遲積分器的程序部分代碼如下表示:

3 模型的仿真結果

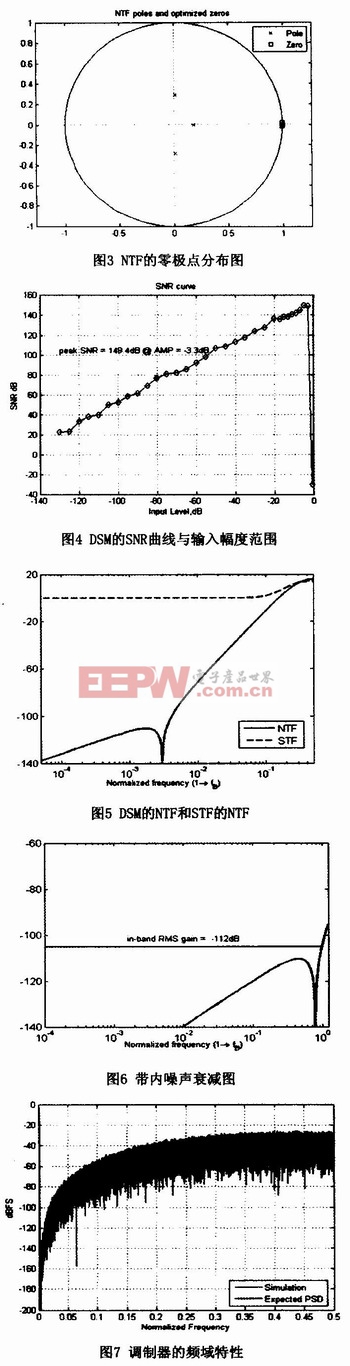

圖3給出的是NTF的極點與零點圖。很明顯,NTF的零點均勻地分布在信號基帶中,而不是集中在直流頻率處。圖4給出了輸入幅度范圍與SNR。圖5給出了NTF和STF的幅頻響應。可以看到,帶內信號的衰減幾乎是0,而圖6顯示噪聲的衰減小于-110dB,滿足帶內噪聲的要求。圖7給出了調制器的頻域特性圖。圖8給出的是在輸入為42000,時鐘頻率為8.4MHz的verilog硬件描述語言的仿真結果,可以看出經過2μs后結果趨于穩定。

4 結論

本文提出一個用在ADC中的16位的3階8級量化的三階單環Delta-sigma調制器。為了提高電路性能,實現較高的SNR和DR,減少量化噪聲的影響,在設計NTF時采用前饋方式和局部反饋的結構,并進行零點優化,通過這些方法優化了輸出SNR,提高DR,降低量化噪聲,使得電路對于量化噪聲有較好的敏感度。根據仿真結果,這個DSM的峰值SNR可以達到145dB以上,在3階的系統和128的過采樣率下,達到相當高的SNR,之后用Verilog語言對調制器各電路模塊進行建模與仿真。

評論