基于FPGA的通用位同步器設計方案(二)

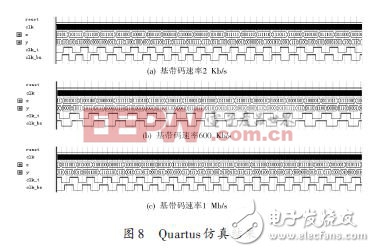

在圖8中,x為基帶碼元序列,y為內插值輸出,clk_t為基帶碼元時鐘,clk_bs為提取出的位同步信號。從圖中可以看到,clk_bs經過定時環路調整,其上升沿逐漸向clk_t的下降沿(即最佳判決點)靠近,且隨著基帶碼元速率的變化,clk_bs也會隨之變化,但其中心頻率與clk_t相同,相位與最佳判決點相差不超過半個碼元周期,可以進行碼元判決,這表明本設計對2 Kb/s~1 Mb/s內的基帶信號,均可實現位同步。

4 結語

本文提出了一種基于FPGA的通用位同步器的設計方案。該設計方案中的同步器在傳統Gardner 算法的基礎上進行了改進,其中,內插濾波器采用Farrow結構,定時誤差檢測采用GA-TED算法,環路濾波器和內部控制器參數可由外部控制器設置,因而實現了較寬速率范圍內基帶碼元的位同步。仿真結果表明,該方案占用FPGA資源較少,并且在實際應用中具有可靠有效性。

評論