將數(shù)據(jù)轉(zhuǎn)換器IP集成到系統(tǒng)芯片簡化設計技術(shù)(一)

系統(tǒng)芯片其他邏輯塊產(chǎn)生的過大噪聲會進入數(shù)據(jù)轉(zhuǎn)換器繼而影響其性能。為確保數(shù)據(jù)轉(zhuǎn)換器與其他邏輯塊很好地隔離,物理集成過程的第一步是在系統(tǒng)芯片中合理確定數(shù)據(jù)轉(zhuǎn)換器的位置。

技術(shù)1:在活躍邏輯(攻擊者)和模擬模塊(受害者)之間保持一定距離

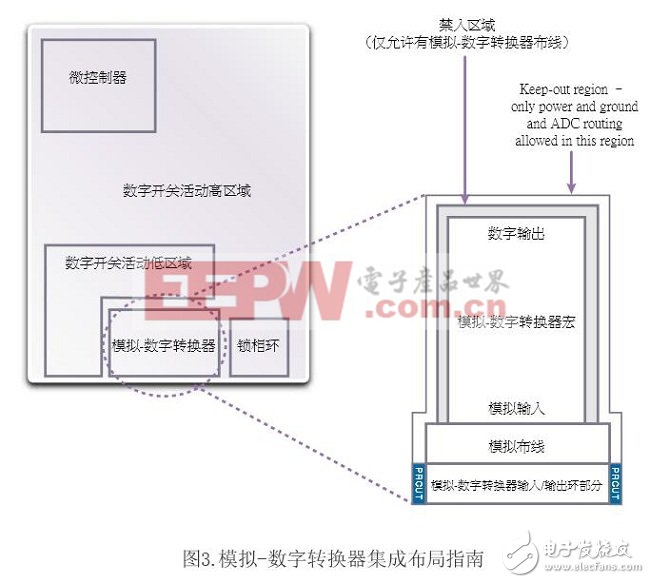

對于普通的模擬-數(shù)字轉(zhuǎn)換器,采用這一技術(shù)可按照圖3中的四個步驟進行操作:

1. 將數(shù)據(jù)轉(zhuǎn)換器(如模擬-數(shù)字轉(zhuǎn)換器)遠離數(shù)字開關(guān)電路;

2. 數(shù)據(jù)轉(zhuǎn)換器數(shù)字接口朝向芯片噪聲較大區(qū)域,而模擬接口朝向芯片較安靜區(qū)域;

3. 將時鐘源(如鎖相環(huán))盡可能靠近數(shù)據(jù)轉(zhuǎn)換器;

4. 如果數(shù)據(jù)轉(zhuǎn)換器臨近區(qū)域有數(shù)字開關(guān)走線或邏輯塊,請設立一個禁入?yún)^(qū)域

(即沒有金屬、晶體管或有源區(qū)的區(qū)域),以便將數(shù)據(jù)轉(zhuǎn)換器與邏輯塊或布線隔離開。

技術(shù)2:數(shù)據(jù)轉(zhuǎn)換器靠近模擬I/O焊盤

進入模擬-數(shù)字轉(zhuǎn)換器輸入的任何噪聲或不需要的信號將被轉(zhuǎn)換器視為“真”信號,繼而出現(xiàn)在數(shù)字輸出中。模擬-數(shù)字轉(zhuǎn)換器能夠區(qū)分的最小電壓(用最低有效位(LSB)表示)決定數(shù)據(jù)轉(zhuǎn)換器的準確度,也是模擬-數(shù)字轉(zhuǎn)換器最大擺幅(FS)及其分辨率(N)的函數(shù)(如以下方程所示)。以0.5V峰-峰最大輸入擺幅的12位單端模擬-數(shù)字轉(zhuǎn)換器為例,最低有效位范圍很小,僅為 122.1μV。

LSB = FS/2N

在如此高的準確度要求下,如果轉(zhuǎn)換的數(shù)字信號(攻擊者)電容耦合(串擾)到模擬-數(shù)字轉(zhuǎn)換器輸入(受害者),數(shù)字輸出信號中耦合的攻擊信號的頻譜含量可能會超出模擬-數(shù)字轉(zhuǎn)換器的噪聲本底值,從而影響系統(tǒng)性能(頻譜純度)。

同樣,串擾數(shù)字-模擬轉(zhuǎn)換器輸出對系統(tǒng)性能產(chǎn)生相似的影響,即轉(zhuǎn)換的數(shù)字信號電容耦合到數(shù)字-模擬轉(zhuǎn)換器輸出可以生成超出數(shù)字-模擬轉(zhuǎn)換器噪聲本底值的頻譜含量。

采用差分輸入的模擬-數(shù)字轉(zhuǎn)換器,或是采用差分輸出的數(shù)字-模擬轉(zhuǎn)換器,都具有較強的抗共模噪聲干擾能力,因為攻擊者均衡地耦合到正負差分信號。為充分利用這種高抗噪聲干擾能力,使用這些數(shù)據(jù)轉(zhuǎn)換器應同時采用正確屏蔽和外部信號布線等設計技術(shù)。

評論