將數據轉換器IP集成到系統芯片簡化設計技術(二)

當數據轉換器需要外部基準時也會出現類似的問題。由于基準決定數據轉換器的滿幅輸入擺幅,如果噪聲或不需要的信號與基準耦合,就會成為數據轉換器輸出信號的一部分。

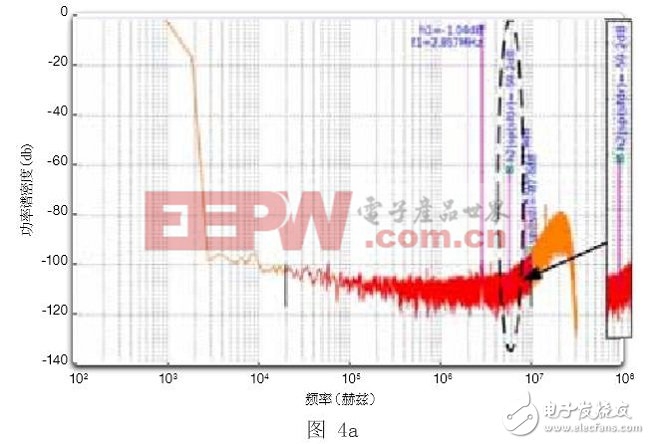

圖 4a顯示了28納米12位Sigma-DeltaIQ模擬-數字轉換器頻譜,可以看到轉換器輸入與基準信號之間有耦合。這會導致第二諧波(h2)能量過大,將總諧波失真(THD)降低近14dB。相反,圖4b顯示的是相同IQ模擬-數字轉換器在耦合消除后的性能,這會使總諧波失真改善,達到 -72dBc。

基準對流經非零電阻(電阻壓降)基準路徑的非零電流造成的壓降很敏感。這一效應會在轉換中產生系統性的偏移(offset)和增益誤差(gain error)。

考慮到這些影響,將數據轉換器正確植入系統芯片之后,下一步就是對轉換器和I/O之間的模擬信號進行布線,同時采用以下技術:

技術3:保持模擬布線路徑簡短

保持模擬布線路徑盡可能簡短,使無關信號不太可能耦合到模擬I/O出或基準中。

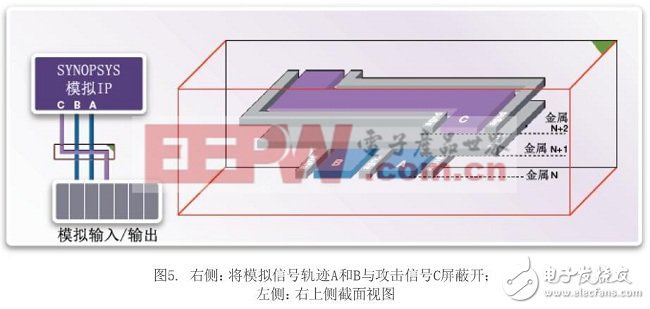

技術4:增加屏蔽

為盡可能減少關鍵模擬信號的噪聲耦合或串擾,特別是在串擾無法避免的情況下,設計人員應在攻擊者和受害者軌跡之間增加屏蔽。圖5介紹了增加有效屏蔽的正確方法:通過中間層(金屬N+1)將以金屬N布線的模擬信號軌跡A和B與以金屬N+2布線的噪聲信號C屏蔽開來,完全覆蓋重疊區域,并與干凈的模擬接地電源連接。通過在臨近信號增加金屬層走線,可在同層的金屬間(分別是金屬N與N+2)實現進一步屏蔽隔離。

只有在必須的情況下才增加屏蔽,而且是不沿著所有路徑,以避免不必要地增加信號寄生電容。

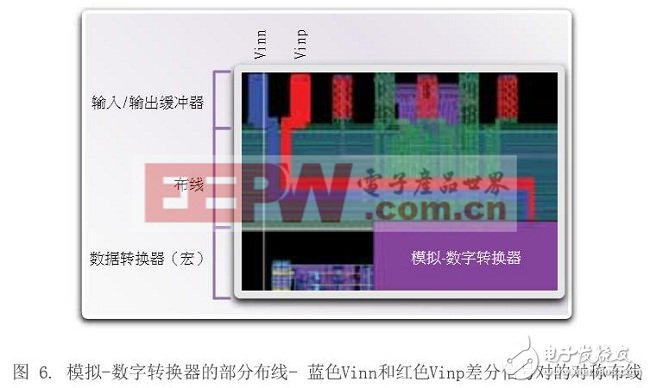

技術5:保持差分走線

為確保模擬差分信號的共模噪聲抑制達到最佳效果,設計師應根據電阻、長度、電容性負載和其他信號的寄生電容耦合、邦定線特征和印刷電路板(PCB)線路等等,對差分信號布線匹配。圖6是從模擬-數字轉換器到I/O匹配后的輸入(紅色Vinp和藍色Vinn)布線。

技術6:限制電阻壓降或阻抗

可通過以下方式確保布線串聯電阻不超過數據轉換器提供商注明的最大電阻值:

△盡量縮短布線距離

評論