將數據轉換器IP集成到系統芯片簡化設計技術(二)

△盡量使用多個金屬層走線

△使用大量過孔進行連接

數字輸出/輸入布線還要求認真仔細地部署。但是,由于布線是在自動數字集成流程中處理,它們的部署自然需要遵循相應的技術,因此不在本文討論之列。

3. 保持低時鐘抖動

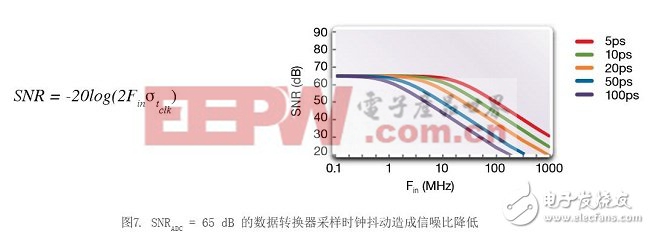

基于數據轉換器的系統性能,如通訊接口,取決于采樣時鐘的質量。模擬-數字轉換器信號采樣瞬間的不確定性增加了轉換噪聲,因而降低了轉換器性能。采樣瞬間的不確定性稱為“抖動”。時鐘抖動(σtclk)決定了數據轉換器可達到的最大理論SNR(信噪比)值。圖7顯示信噪比是采樣時鐘抖動的一個函數,將信噪比、時鐘抖動和信號頻率(Fin)關聯起來。以模擬-數字轉換器固有的65dB信噪比(SNRADC)為例。

從圖7可以看出,采樣時鐘抖動對轉換性能(信噪比)的影響與系統處理低頻率信號無關。但是,采樣時鐘抖動的影響隨著所處理信號的頻率增強而增加

因此,系統芯片設計師在設計中必須考慮到這種影響,可以采用以下技術保證采樣時鐘質量:

技術7:將時鐘源靠近數據轉換器

將鎖相環靠近數據轉換器,可降低外部信號耦合到時鐘線并造成時鐘抖動的可能性。

技術8:檢查時鐘沿速率

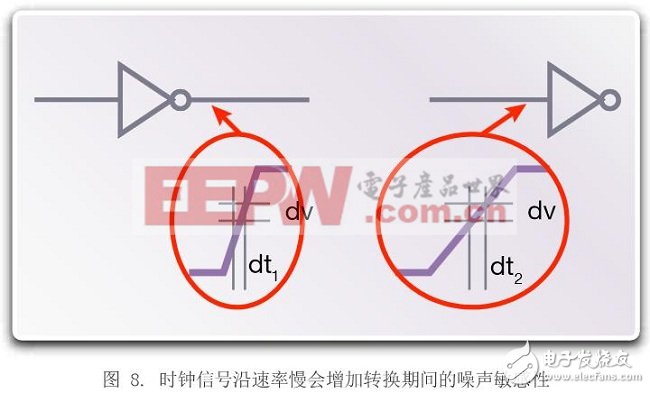

對于時鐘路徑上的任何電路而言,應保證有足夠的驅動強度限制時鐘的轉換速率。時鐘沿轉換時間長會增加噪聲敏感性,因而增加抖動(如圖8所示)。根據經驗,~100ps的轉換時間是適當的。

評論