3D器件堆棧的新型組裝方法

半導體封裝的下一個重大飛躍將需要一系列新技術、工藝和材料,但總的來說,它們將使性能得到數量級的提高,這對于 AI 時代至關重要。

并非所有這些問題都得到完全解決,但最近的電子元件技術會議 (ECTC) 讓我們得以一窺自 ChatGPT 的推出震驚科技界以來,過去幾年所取得的巨大飛躍。AMD、TSMC、Samsung、Intel 和許多設備供應商詳細介紹了混合鍵合、玻璃芯基板、微通道或直接冷卻冷卻以及通過背面電源方案散熱方面的改進。

“AI 改變超級計算機/高性能計算空間的方式令人驚嘆,”AMD 高級副總裁兼企業研究員 Sam Naffziger 在關于 AI 計算的演講中表示。“ChatGPT 和 Geminis 已經攝取了整個互聯網數據世界并訓練了模型,但高質量的文本數據已經被完全消耗掉了。AI 變得越來越智能的方式是通過稱為后訓練和測試時計算或思維鏈推理的方法,這是模型相互檢查、生成合成數據并迭代響應并產生更深思熟慮的結果的地方。盡管智能的每一次增長都非常有價值,但需要多兩到三個數量級的計算才能獲得智能的線性回報。因此,對計算的需求將繼續增長,而這樣做是為了降低成本,而這正是我們行業非常擅長的。我們改進我們的制造流程。我們的產量越來越高,產量提高,成本下降。隨著這一趨勢的持續,芯片制造的創新,尤其是封裝的創新將發揮核心作用。

ECTC 詳細介紹的主要進展包括:

Intel 的混合鍵合低至 1μm 間距;

臺積電對 CoWoS 的直接冷卻,包括 4 個 SoC 和 6 個 HBM;

ITRI/Brewer Science 的 10 層 RDL,采用聚合物/銅混合鍵合;

佐治亞理工學院的小芯片作為冷卻劑,通過 TSV/硅柱進行液體冷卻;

Corning/Fraunhofer IZM 用于光收發器的玻璃波導;

三星用于移動處理器和 DRAM 的銅基加熱塊,以及

Imec 的熱通量與熱點的 3D 多芯片仿真。

熱切屑

的液體冷卻隨著強制空氣冷卻達到極限,切屑層的液體冷卻開始形成。“我們正在設法使用高速風扇冷卻高達 1,000 瓦的設備,而風扇功率消耗了大約 20% 的服務器機架預算,而我2R 損失占 10% 到 20%,“Naffziger 說。“所以現在我們有 40% 的電力僅用于輸送電流和提取熱量。這顯然不是構建高效計算系統的方法。這就是推動直接液體冷卻無情發展的原因,這種冷卻在泵和冷凝器中有一些電力開銷,但比具有巨大散熱器的高速風扇要小得多。

在會議上,臺積電的 Yu-Jen Lien 介紹了一種稱為硅集成微型冷卻器 (IMEC-Si) 的液體冷卻架構,該架構正在使用有機中介層 (CoWoS-R) 上的 1.6X 標線大小的測試車輛進行可靠性測試。該散熱器旨在模擬 4-SoC、8-HBM 封裝,使用 40°C 水流速 10 升/分鐘,可以耗散超過 3,000 瓦的均勻功率。這種液體冷卻方法可提供卓越的冷卻效果(高達 2.5 W/mm)2功率密度)相對于具有熱界面材料方案的間接液體冷板。

圖 1:使用 10 L/min 水(下圖)的直接液體冷卻 CoWoS 比使用 TIM、蓋子和冷板配置的 CoWoS 散發更多的熱量。來源:IEEE ECTC [1]

TSMC 的組裝流程應用了一個保護層來覆蓋 SoC 背面的銅柱陣列。將組件翻轉到載體晶片上,然后進行 C4 碰撞。翻轉和保護層去除后,傳統的 CoWoS 流程之后,在 SoC 周邊分配彈性體密封劑。密封劑可最大限度地減少翹曲并密封芯片到蓋子的區域。“回流焊后,將具有單個入口和出口的歧管組裝到集成系統上,該歧管旨在在多個冷卻室之間實現均勻的流量分布。”[1]

臺積電配備 4 個 SoC 和 6 個 HBM 芯片的 3.3X 掩線測試車經歷了 160-190μm 的翹曲范圍,這會導致蓋子和 SoC 芯片之間的流速和輪廓發生變化。該封裝通過了氦氣泄漏測試和早期可靠性測試。

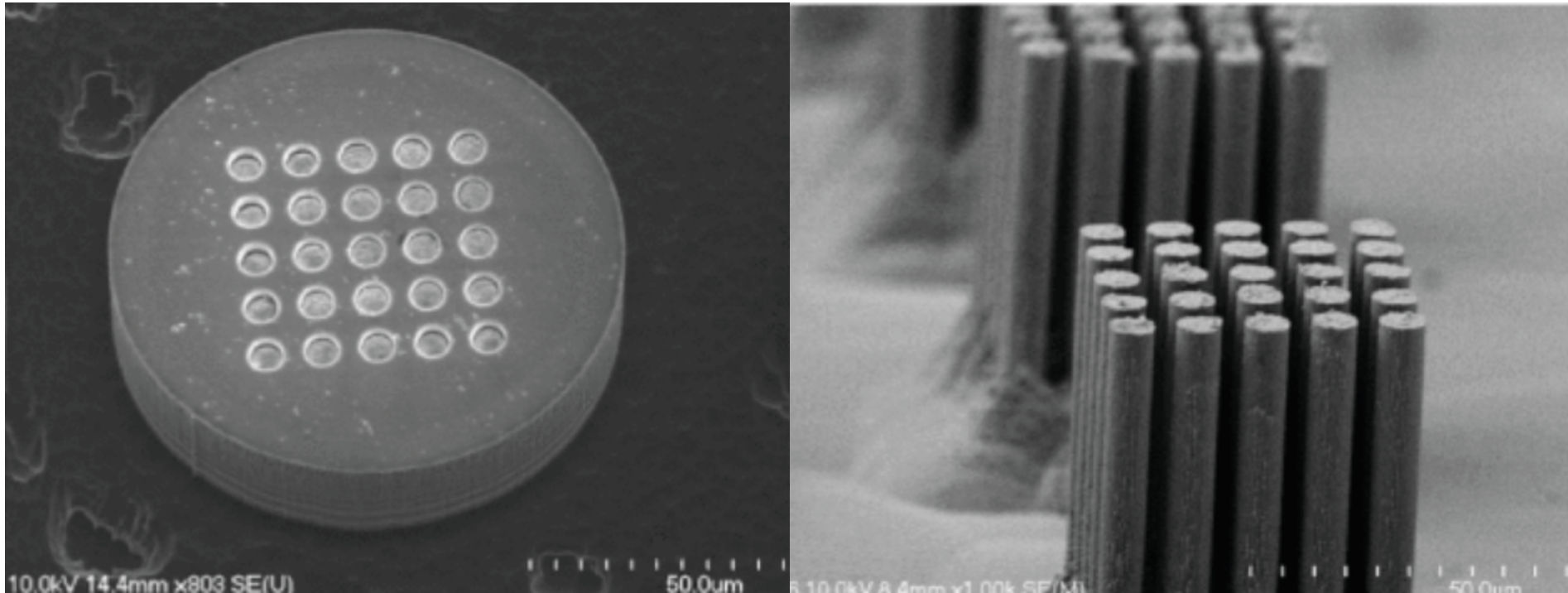

對直接切屑冷卻的需求非常迫切,以至于佐治亞理工學院提出了一個新穎的概念,即小芯片作為冷卻劑。“想象一下,我們設計的小芯片成為現成開源社區的一部分,這些小芯片設計具有不同的冷卻能力,比如說具有不同的直徑、間距,但也具有不同的 TSV 設計,”佐治亞理工學院 3D 包集成中心主任 Muhannad Bakir 說。“我們可以在該結構中構建獨特的 TSV 結構、獨特的冷卻結構以及獨特的其他功能,以幫助熱能和電力輸送。因此,它實際上只是成為堆棧中的混合粘合解決方案。Bakir 的小組展示了由硅制成的微型翅片引腳散熱器,具有 5nm TSV(見圖 2),可以冷卻 >300W/cm2。[2]

圖 2:微流體冷卻包括硅散熱器和用于芯片-芯片連接的硅通孔。來源:IEEE ECTC [2]

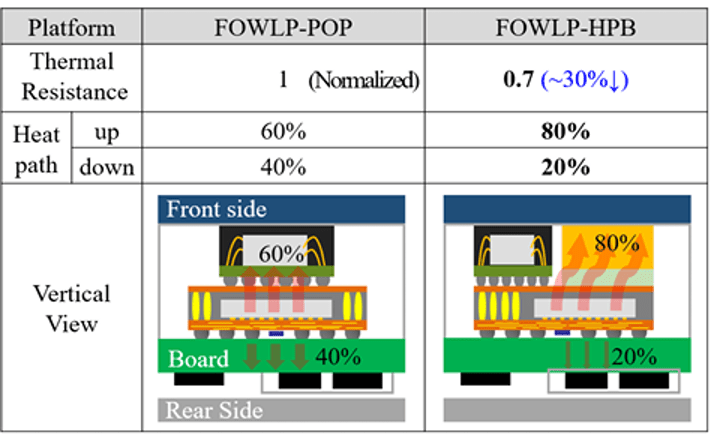

另一種冷卻方法在 Samsung 用于移動應用的新型架構中的應用處理器頂部放置了一個加熱塊(見圖 3)。[3] Kyung Don Mun 及其同事探索了一種非對稱內存和處理器結構,該結構為處理器、內存和基于銅的熱路徑模塊的放置提供了設計靈活性。

圖 3:從邏輯結構上的對稱存儲器(左)切換到處理器上帶有銅熱路徑塊的非對稱結構(右),改善了具有背面供電網絡的 2nm 柵極全環繞邏輯器件的散熱效果。來源:IEEE ECTC [3]

具有背面供電網絡的應用處理器的 2nm 柵極全環繞晶體管結構需要將模塊的散熱提高 20%。三星使用 Ansys 的有限元模型來識別高風險區域并仿真翹曲。“RDL 圖形設計優化對于這種異構封裝設計尤為重要,因為薄 RDL 容易受到熱機械應力集中和裂紋失效的影響,”Mun 說。選擇具有更寬圖形寬度和更長圖形長度的再分布層減少了翹曲。成型材料、雙面 RDL 和熱界面材料得到了進一步改進,以實現更高的導熱性和散熱性。

混合鍵合

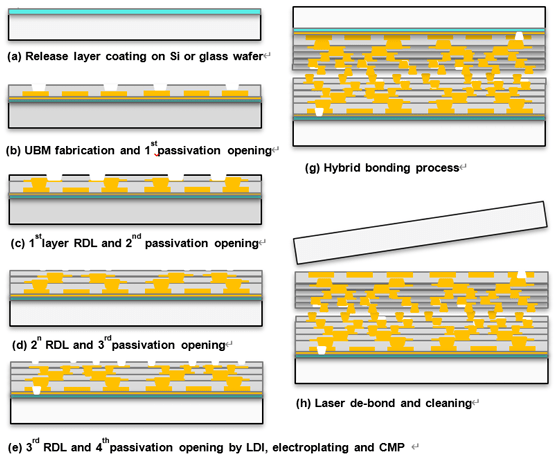

細間距多層有機再分布層 (RDL) 作為硅中介層和層壓襯底的可行替代品越來越受歡迎。這種轉變是由 RDL 以低成本提供高速互連的能力推動的。工業技術研究所 (ITRI) 和 Brewer Science 展示了聚合物/銅 RDL 的五層堆疊,然后是銅-銅混合鍵合,針對高速數字應用中的高 I/O、低回波損耗和低插入損耗。[4]

圖 4:聚合物/銅堆積的再分布層之后是具有受控翹曲的 Cu-Cu 混合鍵合。來源:IEEE ECTC [4]

在玻璃載體晶圓上構建線/空間 RDL (4 至 10μm L/S)后,使用負色調光刻膠和 i-line 曝光對低 k 聚合物 (2.5) 進行圖案化,然后進行蝕刻、用鈦阻擋層和銅填充焊盤,然后用銅 CMP 平坦化。混合鍵合使用 300°C (1.06 MPa) 的熱壓鍵合,然后通過 UV 激光進行載體晶圓解鍵合。低模量、高熱穩定性和低吸濕性等聚合物特性旨在實現多層 RDL 堆棧的低翹曲。

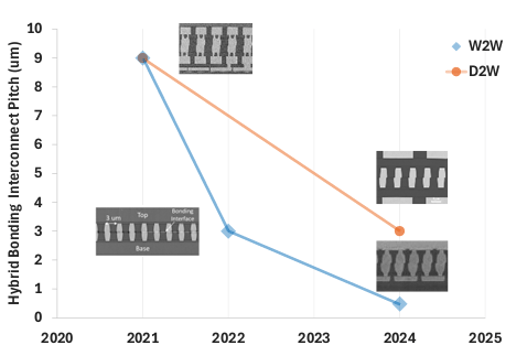

近年來,使用傳統電介質(SiO2基/銅)的混合鍵合的間距縮放已經從10μm(制造中)擴展到1μm(研發中)。Intel 高級首席工程師 Adel Elsherbini 和他的同事討論了實現此類擴展所需的一些功能。[5]

圖 5:Intel 使用混合鍵合的研究結果。來源:IEEE ECTC [5]

他們的論文指出,系統架構通常決定是選擇晶圓到晶圓 (W2W) 還是晶片到晶圓 (D2W) 鍵合。晶圓到晶圓鍵合的主要限制是它需要相同大小的小芯片鍵合。該技術更成熟,可實現更精細的間距。晶片到晶片鍵合沒有尺寸限制,只使用已知良好的晶片。“對于 C2W 應用,隨著 HB 間距繼續擴展到 1μm 及以上,貼裝精度要求突破了當前一代芯片鍵合機的極限。為了確保電氣連續性,整個小芯片區域需要達到相同的精度水平,低至幾十納米。類似于 W2W 鍵合的跳動和變形控制,芯片內精度控制變得越來越重要,“作者說。

“傳統的貼裝精度標準,如小芯片中心或最差角錯位,已經不夠用了。D2W 工藝控制在鍵合過程中變得越來越復雜,以更多地關注每個小芯片級別的翹曲控制、芯片成型和鍵合波傳播控制。另一方面,為了量化晶粒內部鍵合精度,需要新的對準標記策略和更好的鍵合后精度測量計量,以了解從芯片制備一直到鍵合的小芯片級變形行為。作者指出,紅外剝離可以重復使用硅載體晶圓,從而降低擁有成本。

使用背面電源

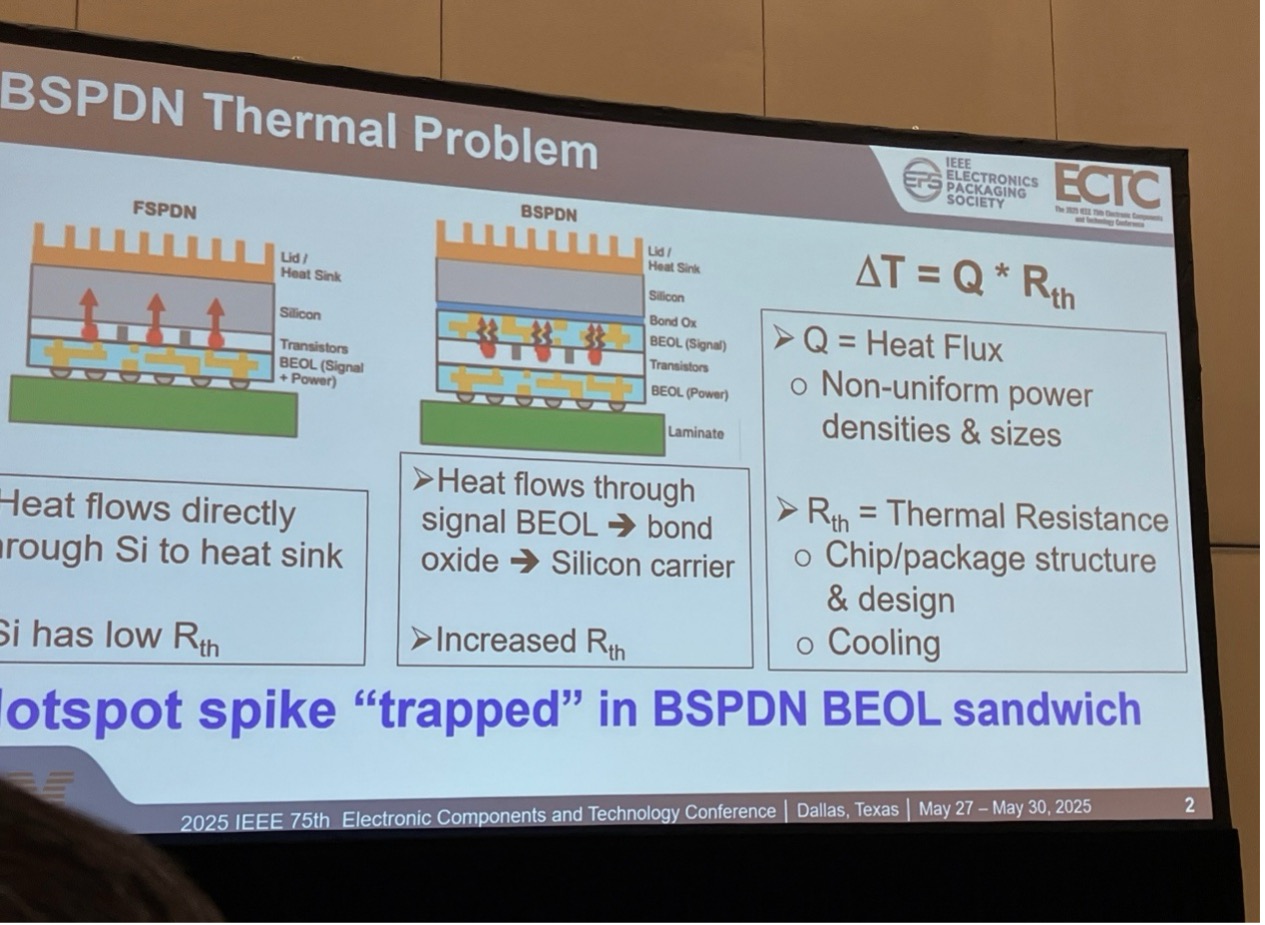

去除熱量背面供電是一種新穎的互連方案,它在晶圓背面構建供電網絡,以顯著降低與向晶體管供電相關的電壓下降。頂部的互連器僅可自由傳輸信號,從而提供許多電氣優勢。

然而,相對于標準互連堆棧,這種新方法加劇了熱點問題(見圖 6)。“如果你從正面的相對視圖來看,晶體管中產生的所有熱量都會直接進入硅片,到達散熱器或冷板,”IBM 研究院高級技術人員 Dureseti Chidambarrao 說。“但還有一個額外的不幸情況,你喜歡背面的電源——因為你把電源和信號分開了,所以這是一種不那么復雜的制造方式——但我們現在面臨著這個挑戰,試圖從這種堆棧中去除熱量,因為熱尖峰和熱電路被困住了。”

圖 6:背面電源會感應出新的熱流模式,因為有源器件夾在金屬堆棧之間。來源:Laura Peters/半導體工程

IBM 開發了一個各向異性模型,可以準確計算通過后端堆棧的熱傳遞,同時考慮材料屬性。該 AI 模型將設計與互連堆棧中的本地功率密度、工作負載和材料屬性聯系起來。“你拿 GDS 文件,它實際上會一起計算多個級別和多個層的平均屬性,這樣你就可以在每個給定位置獲得正確的 [傳熱] 平均屬性。現在你有辦法計算每個瓷磚,而且你可以越來越細化它,“Chidambarrao 說。

在設計階段考慮此類熱因素的重要性怎么強調都不為過。“封裝和芯片正在相互作用,并且已經變得非常緊密耦合,因此這是一個完整的系統技術優化問題,你必須擔心設計中的熱問題,”他說。“這尤其必須發生在背面電源上,我什至沒有想象到最糟糕的事情——在 3D 芯片上放置背面電源。如果這是你想做的,那么解決方案顯然要嚴格得多。

背面供電已經被設計到芯片中。“我們預計明年將首次在產品中實現背面電源,”imec 的主要技術人員兼熱建模和特性研發團隊負責人 Herman Oprins 說。“雖然背面電源最初是無源結構,但進一步這也將用于包括信號時鐘和其他功能。方法有很多種,但最重要的是你需要通過 nanoTSV 連接正面和背面。

NanoTSV 要求將硅減薄到至少 300nm,可能小于 100nm。此外,還需要進行詳細的建模來了解此類設備的冷卻需求。

Oprins 說:“如果你有一個局部熱點和超薄硅,你的溫度實際上會升高,因為你有更少的電量(硅)來分散它。另一方面,背面有金屬堆棧,因此這種密集的金屬陣列可能有助于設備的熱量擴散。

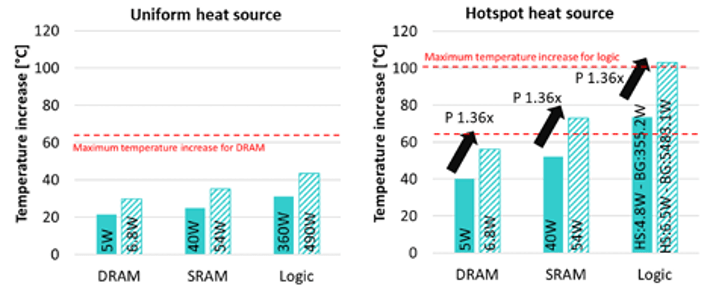

Imec 之前表明,實施背面電源會造成 10% 到 30% 的熱損失 (ECTC 2024)。今年,Oprins 的小組使用 BSPDN 模擬了堆疊邏輯對內存或內存對邏輯的熱效應。這些仿真包括芯片的面對面混合鍵合和背對面鍵合,結合使用玻爾茲曼傳輸方程和蒙特卡洛仿真。仿真說明了均勻芯片加熱與熱點影響之間的溫升差異(見圖 7)。

圖 7:具有均勻器件加熱(左)的器件溫度升高與有額外熱點的器件。來源:IEEE ECTC [7]

“堆棧中邏輯和內存芯片的順序對熱性能的影響更大,”Oprins 說。“由于靠近冷卻,Logic-on-top 導致邏輯溫度較低,但由于堆棧中的高熱耦合,內存溫度較高。”多層 memory-on-logic 表明,BSPDN 的熱影響減少了多個芯片堆疊。在這種情況下, logic on top configuration 受 memory die temperature 的熱限制,而對于 memory-on-top configuration,logic temperature 是限制因素。該論文總結道:“更高效的冷卻表明,3D SoC BSPDN 的熱性能得到了顯著改善,從而實現了具有校準功耗的內存邏輯配置。[7]

Oprins 強調了液體冷卻的重要性。Oprins 說:“看看 3D 架構,如果你每個芯片堆疊 5 個芯片,比如說耗散 100 瓦并使用傳統的空氣冷卻,那么你最終得到的最大結溫遠大于 500°C。如果集成冷板,則最高結溫約為 250°C。 然而,如果你能以某種方式在電堆內開發層間冷卻,那么突然之間就有機會真正將溫度降低到 50°C 左右,“imec 的 3D 電堆模擬說。

共封裝光學器件

行業對更快數據網絡和設備接口速度的需求正在急劇增加。數據中心機架內部的一個關鍵推動因素是將光學引擎與 GPU 和 HBM 集成到同一個封裝中。“借助共封裝光學器件 (CPO),我們有機會將電氣互連與光學連接集成到一個封裝中,”ASE 研究員 CP Hung 說。“這是該行業的新里程碑。通過將光學引擎移到更靠近處理器的位置,我們將每根光纖的 200 Gb/s 提高到 6.4Tb/s,帶寬增加了 32 倍。

盡管 CPO 做出了承諾,但未知數仍然存在。“CPO 肯定會發生,而且這種勢頭肯定會推動它盡早發生,”ASE 工程、營銷和技術推廣高級總監 Mark Gerber 說。“使用 CPO 時,熱側和翹曲側都存在敏感性。重要的是,該行業希望保持當今存在的光學引擎的可插拔(即可替換)方面。但是,雖然 plug-able 很容易切換,但它們并不容易掌握。

在 ECTC 上,ASE 展示了其用于 ASIC 交換機和以太網/HBM 共封裝光學平臺的模塊化平臺。

熱仿真在選擇先進封裝散熱堆棧的架構、工藝和材料方面也發揮著關鍵作用。“從歷史上看,在單片芯片集成中,封裝設計和散熱器的熱仿真是按照通過/不通過的方式進行的,”Amkor Technology 的熱仿真工程師 Tom Nordstog 說。借助多小芯片封裝,仿真在封裝設計的早期階段發揮著更明顯的作用。“熱仿真是一項風險/回報練習,旨在選擇最終設計。理想情況下,封裝的熱設計發生在芯片設計之前。我們看到最積極的客戶在這些早期階段就采用熱仿真。

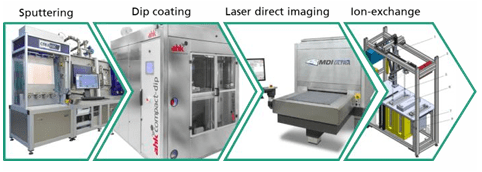

康寧和Fraunhofer IZM提出了一種可擴展的“平面2D波導電路',可以通過減少對光纖電纜終端和手動組裝的需求,為未來幾代CPO解決方案減少所需的空間、復雜性和成本。[8]該團隊使用 460 x 303 毫米熔融成型玻璃面板制造了具有波導布局的單模板級互連,旨在滿足將 1024 個光鏈路從面板連接到 CPO 模塊的光互連要求,用于 102.4 Tb/s 數據中心交換機應用。Fraunhofer IZM 工程師設計了工藝流程(見圖 8),其中包括將單模波導集成到玻璃中的熱離子交換工藝,與 1310nm 波長的單模光纖的光模式相匹配。移除掩模后,執行第二個反向離子交換過程步驟,將波導的核心埋在玻璃表面以下,以減少傳播損耗。

Brusberg 說:“為了與玻璃波導面板的光纖連接,組裝了 MPO-16 適配器,并將玻璃波導電路集成到 1U 機架機箱中,以展示僅 0.7 mm 的扁平外形。這種新穎的方法可以為基于 PCB 的光收發器鋪平道路。

圖 8:工藝流程包括金屬沉積、光刻膠涂層、波導成像和離子交換,以將銀擴散到圖案中。來源:IEEE ECTC [8]

引用

Y-J Lien,“集成在 CoWoS 平臺上的直接到硅液體冷卻”,IEEE 電子元件和技術會議,2025 年 5 月,正在出版。

Yan 等人,“面向 3D IC 的 TSV 兼容微流體冷卻”,IEEE Transactions on Components, Packaging and Manufacturing Technology,第 15 卷,第 1 期,第 104-1,12 頁,2025 年 1 月,doi:10.1109/TCPMT.2024.3516653。

D. Mun 等人,“一種增強散熱的移動應用中設備端 AI 的新型架構”,IEEE 電子元件和技術會議,2025 年 5 月,正在出版。

-H. Lee 等人,“通過可轉移銅/聚合物混合鍵合實現具有新穎結構的分層多層和堆疊通孔,用于高速數字應用”,IEEE 電子元件和技術會議,2025 年 5 月,正在印刷中

Chang 等人,“先進 BEOL 堆棧等效熱特性的熱建模和分析”,IEEE Transactions on Components, Packaging and Manufacturing Technology,doi:10.1109/TCPMT.2025.3564833。

Elsherbini等人,“通過低于1um間距的混合鍵合和先進的硅載體技術實現的Mid-BEOL異構集成,用于AI和計算應用”,IEEE電子元件和技術會議,2025年5月,正在出版。

R. Chowdhury,“Backside Power Delivery and Chiplet Architectures中后端線熱阻的快速準確機器學習預測”,IEEE 電子元件和技術會議,2025 年 5 月,正在出版。

Brusberg,“用于面板和共封裝光收發器之間板級光互連的大規模玻璃波導電路”,IEEE 電子元件和技術會議,2025 年 5 月,正在出版。

評論