H.264視頻解碼芯片中與濾波相關的存儲器的設計

2 DRAM 的規劃與設計

DRAM 是一種成本低、容量大、應用廣泛的存儲介質, 對大規模數據的操作十分迅速。然而由于DRAM 中有一個Row 的概念。在操作不同的Row 的情況下DRAM 要先關閉當前的Row, 同時再激活所需的Row,這樣就造成了很多的overhead。試想讀取同一Row 的10 個數據與分別處于10 個Row 的10個數據,后者的時間耗費將會是前者的5~6 倍。因此DRAM 不適合對隨機的分散的數據存取。

由于Row 的存在, 對DRAM 中的數據結構的設計就顯得尤為重要。要盡量減少不同Row 之間的訪問,這樣才能提高數據的存取效率。本次設計中采用位寬為64 位的DRAM, 恰好可以存放8 個點的像素值。一幅圖像亮度Y、色度UV 分別存放在一個連續的空間中。

H.264 解碼后的最后圖像存入DRAM 中,顯示模塊不斷的從DRAM 中取出數據送到顯示器, 運動補償單元也要從DRAM 中取出參考幀的數據。因此DRAM 的帶寬尤為緊張。合理地分配DRAM 的帶寬是設計中要考慮的一個重要方面。由于很多模塊都要求對DRAM 進行操作, 為了有效地對DRAM 進行管理,設置了DRAMCONtrol 模塊來對DRAM 進行控制。

3 DRAMControl 模塊的設計

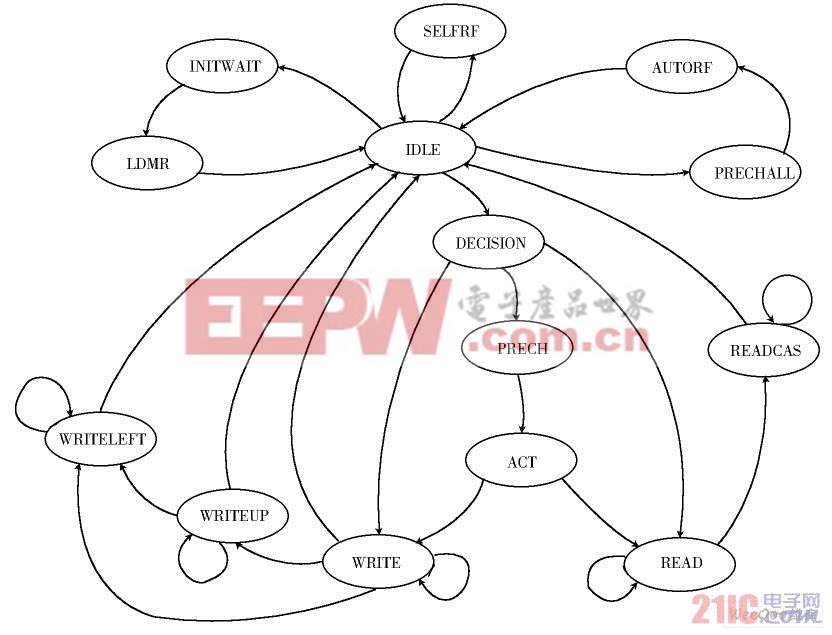

DRAMControl 模塊控制著DRAM 與外面其它模塊的交互,是DRAM 與外部其它模塊的接口。主要的功能包括DRAM 的自動刷新、DRAM 的命令的產生等。因為DRAM 工作時的狀態多,本次設計中采用狀態機的方式來實現。其中狀態圖如圖2 所示。

圖2 DRAMControl 中的狀態轉移圖

設計中采用了均勻刷新的方式, 每隔一定的時間, 經過“IDLE → PRECHALL → AUTORF →IDLE”的過程就完成一次刷新。狀態轉換的主體是讀寫操作過程,判決狀態(Decision)占用一個時鐘周期判斷當前操作所要執行的Row 是否處于激活狀態,如果沒有激活則要先關閉當前處于激活狀態的Row,再激活所需的Row(通過PRECH 和ACT 狀態完成);如果已經激活,則直接進行讀寫操作。對于寫操作,針對H.264 中濾波結束后要更新上邊宏塊,左邊宏塊以及自身宏塊的數據來設計了WRITEUP 或WRITELEFT 和WRITE 這三個狀態寫入DRAM,而且這些狀態之間實現了時間上的無縫連接,構成了一個完整連貫的BurST 寫操作; 如果上邊宏塊的數據或左邊宏塊的數據塊處于與待濾波宏塊的數據塊不同的Row 中,則在WRITEUP 或WRITELEF 狀態實現不在本Tile 中數據塊的寫操作,這種情況的寫效率顯然比在同一個Row 中的時候下降了, 但這是不可避免的, 當宏塊處于本Row 的最左邊或最上邊的時候,其上邊宏塊數據或左邊宏塊數據塊必然是屬于其它Row 的。本次設計中,DRAM 一個地址存本block 和下一個block 的同一行, 因此這樣就最多的避免了跨Row 的操作。對于其它情況的寫操作,使用WRITE 狀態完成。

評論