AMD 助力全國大學生 FPGA 創新設計競賽

由 AMD 作為主要協辦方之一的“全國大學生嵌入式芯片與系統設計競賽—— FPGA 創新設計競賽”日前落下帷幕。這是目前國內 FPGA 競賽領域最高水平競賽之一,旨在提高學生在數字系統設計領域尤其是可編程邏輯器件應用領域的創新實踐能力,培養具有創新思維、具備解決復雜工程問題能力且富有團隊合作精神的優秀人才,推進高校與企業人才培養合作共建。

本文引用地址:http://www.104case.com/article/202402/455421.htm作為競賽的協辦方,AMD 為競賽提供了一系列具有挑戰性和前瞻性的賽道選擇,激發參賽選手的創造力和解決問題的能力。本次競賽 AMD FPGA 賽道吸引了來自國內 200 多所高校的近千支隊伍,近三千名本科及研究生同學參與其中。此外,AMD 還為參賽隊伍提供了多樣化的器件,包括 Spartan 7 FPGA 系列、Zynq UltraScale+ MPSoC 系列以及最新的 Versal 自適應 SoC 系列器件,展現了 AMD FPGA 技術在大學教育和學術創新的廣泛使用。

AMD 競賽主要考察參賽作品的理論創新與應用場景創新。由 AMD FPGA 和自適應 SoC 器件提供支持的競賽作品涵蓋了模式識別、算法加速、機器控制等多個領域。一些作品在傳感器融合、通信技術、圖像處理等方面取得了顯著成果。例如既有創造性地利用FPGA 數字信號處理的優勢實現了藝術的跨界組合;又有成功落地于自動化圖書館、高性能儀器設備、高速目標識別等實際場景。

AMD 賽道作品展示(部分)

面向自主智能體感知與協作的多移動機器人控制器設

多自主移動智能體( AMR )是目前工業自動化中種類最多、應用最廣的一大類自主智能體,它可以自動完成貨物搬運,多 AMR 系統目前已成為企業自動化生產系統的重要組成部分。在人機共存的復雜工業場景下,目前多 AMR 系統主要面臨寬闊路徑下運輸效率低、軟件系統的通用性和適應性差、硬件系統成本高等問題。

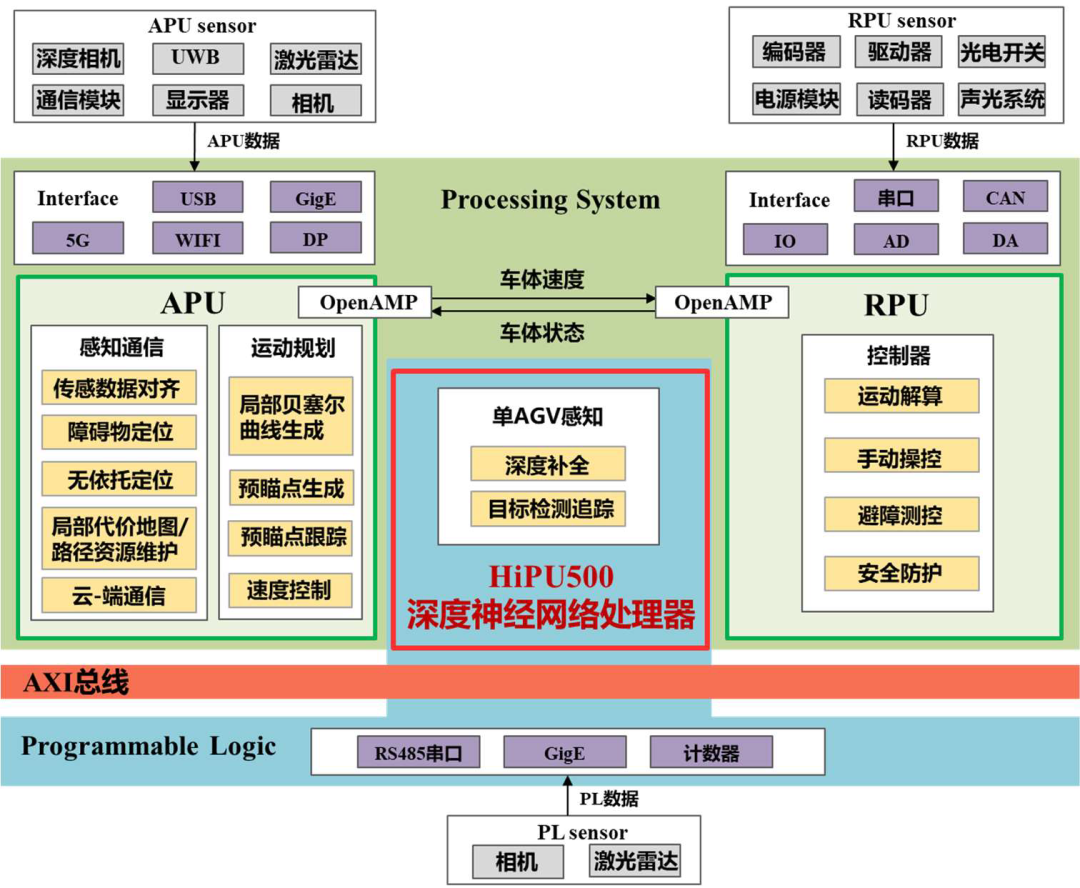

來自西安交通大學團隊設計了一種面向端云協同的多 AMR 控制器以解決上述問題控制器采用異構多核處理器實現,充分利用 Zynq MPSoC 中多核 PS、PL 等資源,合理分配計算負載,在軟件和硬件兩方面實現算法加速。在 PS 側的 APU 上執行通行、規劃以及定位算法,PS 側的 RPU 主要運行底層控制和安全邏輯程序,APU 和 RPU 之間通過 OpenAMP 的框架進行通信和數據交互;在PL 側通過 FPGA 擴展更多靈活接口以及自主研發的 HiPU 神經網絡加速 IP 對目標檢測以及深度補全等算法進行加速,最終在一顆 Zynq MPSoC ZU3 有限資源上完成 AMR 的智能計算。

基于Zynq 7000的多波束高速數字接收機系統

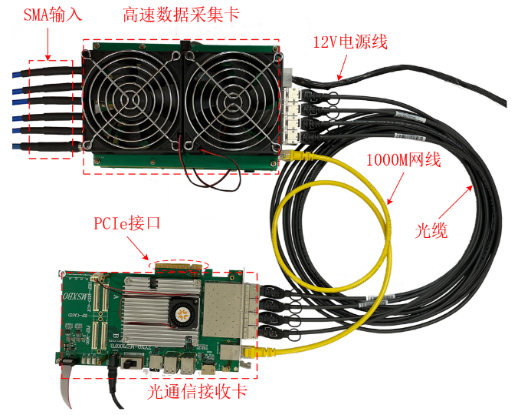

針對射電觀測對于獲取時域數據的需求,來自三峽大學的團隊利用 Zynq 7100 器件實現了一種 4 通道高速數據采集和處理系統。系統基于 GTX 完成與兩片高性能 ADC 器件之間串行高速通信,具備 60dB 滿量程信噪比、40Gbps 的 SFP+ 數據傳輸帶寬,實現 300MSPS @ 16bit 的直接采樣功能,并通過上位機進行時域數據的展示與存儲。

基于 Zynq 的多算子融合顯微鏡電動聚焦系統

在常見的顯微鏡觀測領域,往往需要通過粗、細調焦獲取足夠清晰的觀察圖像,但人工調焦的方式較為繁瑣和消耗使用者精力且存在一定誤差。隨著科技的發展,顯微鏡未來勢必朝著實時成像、多模態成像以及自動智能化的方向發展。而自動對焦技術作為輔助顯微鏡快速清晰成像的重要工具,未來勢必有著廣闊的應用前景。

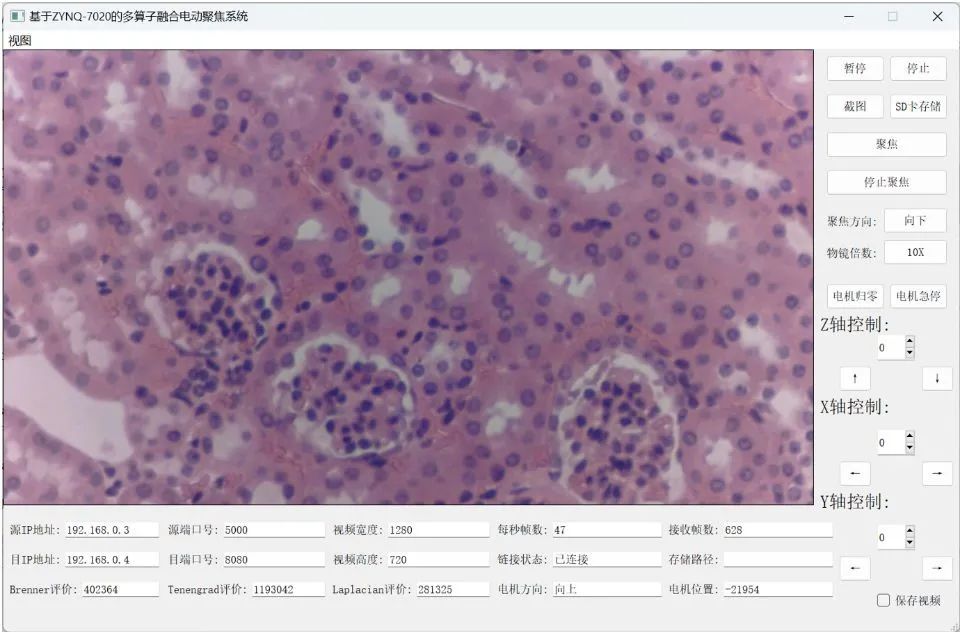

來自華南師范大學的團隊在本次競賽中在 Zynq 7020 器件上實現了高速聚焦成像,動態無參考圖像的失焦量評價、4 路圖像拼接等功能。產品每秒可進行高達 48 次圖像評價,同時在圖像處理消影期間實現電動平臺的移動,不干擾圖像評價進程。

除了已經在實際工程中部署應用的作品,大賽中也涌現出很多結合參賽同學實際生活需求而完成的作品。這些成果富有創意,同時也展現了 AMD FPGA和自適應 SoC 在數字信號處理、高性能、低時延以及 AI加速方面的出色特性。

吉他自動調音器

來自西安電子科技大學的同學利用 AMD Spartan7 器件設計了一套吉他自動調音器。參賽者將采樣到的吉他音量信號經過 FIR、FFT 等信號處理算法監測、頻率分析、消除泛音等過程,并通過定制結構操縱琴頭和琴弦處機械結構實現同步撥弦和調整旋鈕,做到自動且準確地調標準音。校音精度達到 ±0.07cent(±3Hz), 平均只需 11 秒即可完成校音。

面向無人售貨的高通量極速果蔬識別系統

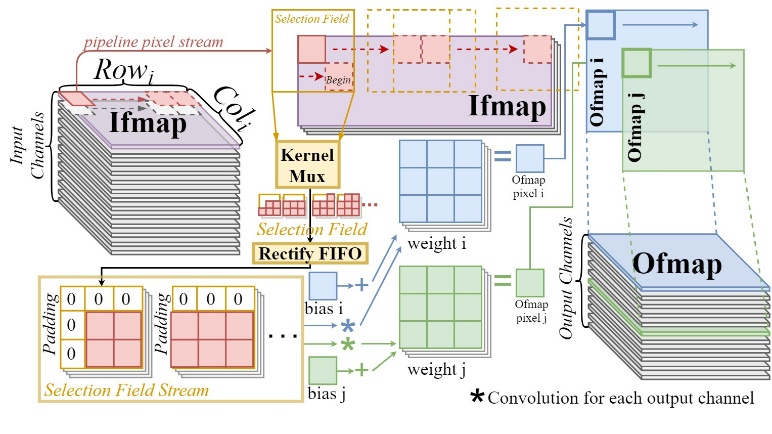

來自武漢大學的參賽者設計了一種針對性的大量果蔬識別算法被設計并將其部署在上硬件開發平臺上。他們為了滿足對同種水果不同品質識別的要求,在基于 FruitVeg81 數據集的自定義精細化數據集上訓練,并利用剪枝、量化等網絡壓縮技術以優化硬件部署。同時結合 Zynq UltraScale+ MPSoC器件的優勢設計了全流水加速架構,從而大幅提升網絡的邊緣推理速度,最終實現了在 495 幀/秒的高幀率下對 125 類不同種類或品質的水果進行識別,準確率達到 95.397%,幀率高達每秒 495.85 幀。

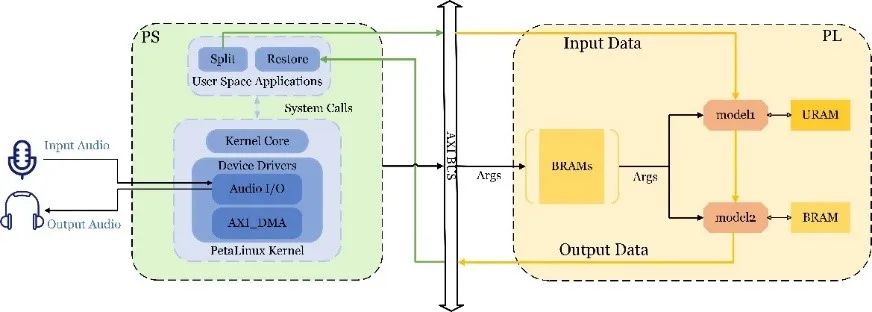

DTLN: 一種基于 Zynq 的雙信號LSTM轉換語音增強系統

來自河海大學的參賽者使用 DTLN 神經網絡降噪模型,模型以雙信號轉換 LSTM 為核心,可以通過學習長期依賴關系更好地捕捉語音信號中的時序信息,從而有效地降低噪音干擾。該作品在 Zynq 平臺上實現了一種基于 FPGA 的協處理器設計,展現了在處理復雜環境下實時降噪任務的出色性能。

FPGA 的靈活編程性為本作品帶來了顯著的優勢,最大化了其異構計算的加速潛力,實現了高效的實時處理。值得一提的是,參賽者在短短三個月內,從零開始利用 Vitis HLS 實現了所有信號處理、神經網絡加速設計、驗證和部署,并在 24bit 量化后通過Vivado、Vitis HLS 和 Petalinux 套件部署到板卡上。該系統脫離了 PYNQ 框架的限制,可以在任何版本的 Vivado 套件上部署并運行,實現音頻的實時降噪處理。

在賽事過程中,AMD 還提供了領先的 FPGA 技術支持和解決方案,為參賽者提供了強大的軟硬件支持。高效的開發工具和豐富的文檔資源,則助力他們充分發揮創新意識,展現自我水平。此外,通過提供技術支持、分享實際經驗,AMD 還與參賽者建立了密切聯系。這種緊密互動的過程為年輕的科技愛好者提供了成長的機會與交流的平臺。

作為大賽的發起方之一,AMD 大學計劃與全國大學生FPGA創新設計大賽已開展深度合作七年,累計支持和培養了上萬名大學生。七年的旅程,見證了 AMD FPGA 賽道從最初傳統的 FPGA 平臺擴展到廣泛普及的 Zynq 平臺這場技術與人才培育的雙贏之旅。放眼未來,期待這些年輕的參賽者在科技領域茁壯成長,為百行百業的發展進步貢獻自己的智慧和力量。

評論