基于FPGA的NAND Flash的分區(qū)續(xù)存的功能設(shè)計(jì)實(shí)現(xiàn)

0 引言

隨著現(xiàn)代技術(shù)的發(fā)展,越來越多的系統(tǒng)采用NAND Flash芯片實(shí)時記錄數(shù)據(jù), 越來越大的NAND Flash容量讓系統(tǒng)可以存儲更大量的數(shù)據(jù)和更長的時間。但是,隨著系統(tǒng)的變得復(fù)雜,對數(shù)據(jù)的存儲也提出了更高的要求。傳統(tǒng)的NAND Flash 控制器每次存儲都是從Flash 的零地址開始,本次存儲任務(wù)結(jié)束后,當(dāng)系統(tǒng)再次開啟存儲后,再次從零地址開始存儲。新的數(shù)據(jù)會寫覆蓋之前的數(shù)據(jù),無法實(shí)現(xiàn)數(shù)據(jù)的續(xù)存,使得NAND Flash使用起來十分不便;而且數(shù)據(jù)反復(fù)地從零地址開始存儲,造成NAND Flash存儲器的使用上的不均衡,影響其壽命[1]。

本文提出了一種基于FPGA的NAND Flash 分區(qū)續(xù)存功能的控制器實(shí)現(xiàn)方法:NAND Flash控制器根據(jù)控制對象的特點(diǎn),將NAND Flash劃分多個分區(qū),利用其自身的某一空間記錄最新的分區(qū)地址信息,控制器在初始化時通過讀取最新的分區(qū)地址信息,自動跳過該分區(qū),在下一分區(qū)開始存儲,同時更新最新的分區(qū)地址信息。通過這種方法,可以靈活地實(shí)現(xiàn)NAND Flash 控制器分區(qū)續(xù)存的功能,解決了數(shù)據(jù)不能續(xù)存的問題,同時也解決了NAND Flash 存儲器的使用的不均衡的問題。

1 電路說明

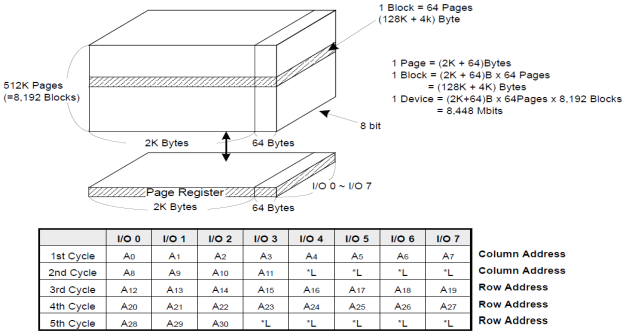

NAND Flash芯片使用型號是三星公司的K9K8G08U0A,單片容量為1 G x 8 Bit。該芯片總共有8 192 個塊(Block),每個塊中含有64 頁(Page),每頁共2112 個字節(jié)(前2 048 個主存儲空間+64 個擴(kuò)展空間)。芯片容量結(jié)構(gòu)如圖1 所示。

圖1 NAND Flash內(nèi)部存儲空間結(jié)構(gòu)圖

FPGA 使用型號為Xilinx 公司Virtex II 系列的XC2V1000,芯片內(nèi)部有5 120 個Slice、40 個乘法器、720 kbit 的RAM 模塊資源、320 個用戶I/O 引腳。

2 NAND Flash控制器設(shè)計(jì)

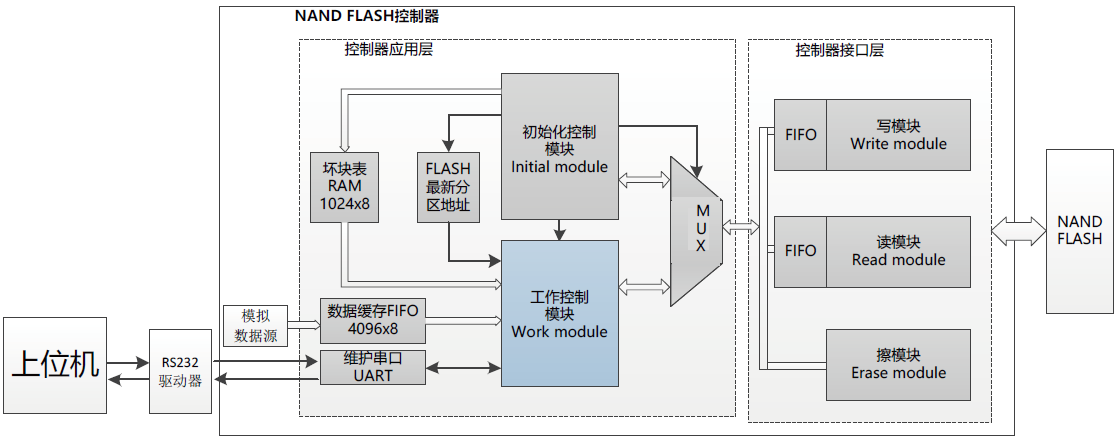

2.1 控制器概述

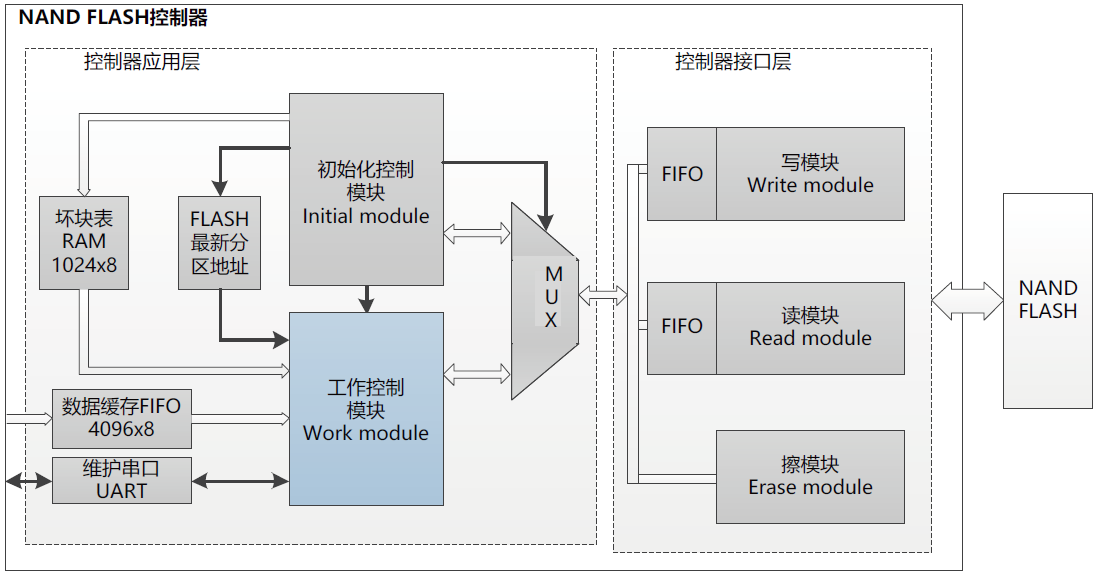

NAND Flash 控制器結(jié)構(gòu)框圖如圖2 所示,一共分為應(yīng)用層和接口層2 部分,接口層負(fù)責(zé)與NAND Flash的讀、寫,擦操作的接口;應(yīng)用層負(fù)責(zé)調(diào)用接口層模塊,同時完成NAND Flash 控制器的控制功能,分區(qū)續(xù)存功能設(shè)計(jì)在工作控制模塊中[2]。

圖2 控制器結(jié)構(gòu)框圖

2.1.1 分區(qū)設(shè)計(jì)

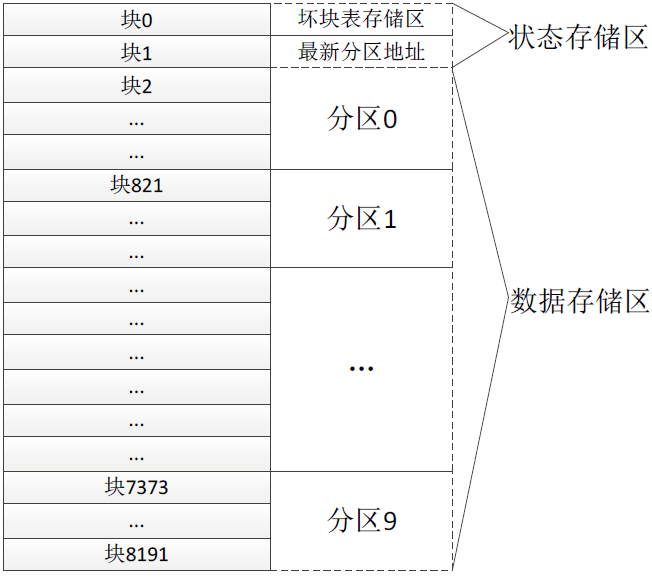

本型號NAND Flash 一共有8 192 個塊,塊地址從0~8 191。其中塊0、塊 1 用作狀態(tài)存儲區(qū),其中塊0 用于壞塊表的存儲,塊1 用于存儲本次數(shù)據(jù)記錄用到的最新分區(qū)的地址信息;塊2~ 塊8 191 作用數(shù)據(jù)存儲區(qū),共計(jì)8 190 個塊,在本設(shè)計(jì)中,將這8 190 個塊分為10個分區(qū),分別為分區(qū)0~9,每個分區(qū)有819 個塊。分區(qū)設(shè)計(jì)結(jié)構(gòu)如圖3 所示[3]。

圖3 NAND Flash分區(qū)結(jié)構(gòu)

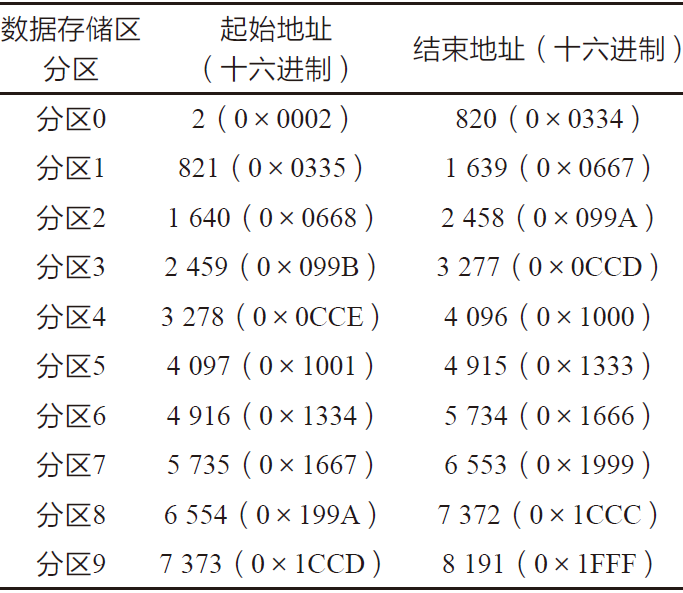

數(shù)據(jù)存儲區(qū)的每個分區(qū)的起始地址和結(jié)束地址見表1。

表1 分區(qū)起始地址與結(jié)束地址

2.1.2 分區(qū)工作機(jī)理

NAND Flash 控制器上電后,需要先讀取到上一次存儲的NAND Flash 的分區(qū)地址信息,所以需要有一塊專門的空間用于存儲該地址[4-5]。在本設(shè)計(jì)中,利用NAND Flash 的塊1 的第0 頁專門的用于存儲該地址信息,使用分區(qū)的起始地址作為分區(qū)的地址信息。

最新分區(qū)的地址信息需要動態(tài)更新。控制器獲取起始地址信息后,根據(jù)分區(qū)大小,自動計(jì)算出下一分區(qū)的首地址作為本次存儲操作的起始地址。控制器先將計(jì)算后的起始地址信息更新至塊1 的第0 頁處,然后從計(jì)算后的起始地址開始,進(jìn)行數(shù)據(jù)存儲操作。當(dāng)數(shù)據(jù)存儲操作超過本次分區(qū)的地址范圍,則控制器在跨分區(qū)時,再次計(jì)算出下一分區(qū)的起始地址,并更新最新分區(qū)地址至塊1 的第0 頁處,從而實(shí)現(xiàn)了最新分區(qū)起始地址的實(shí)時更新[6]。

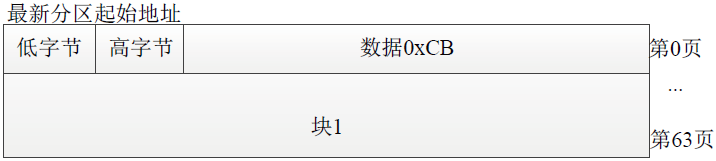

2.1.3 分區(qū)地址的存儲

NAND Flash 存儲器塊1 中的第0 頁為最新分區(qū)的首地址存儲區(qū),存儲的數(shù)據(jù)格式如圖4 所示。第0 頁的第0、1 字節(jié)為最新分區(qū)首地址;第0 頁的其他的數(shù)據(jù)皆為0xCB,該數(shù)據(jù)用于大量數(shù)據(jù)讀取時的檢索,能夠方便地找到最新分區(qū)的首地址存儲區(qū)。

圖4 分區(qū)信息存儲結(jié)構(gòu)

由于塊1 反復(fù)地被更新寫入最新分區(qū)的起始地址,需要估算塊1 的使用壽命:本次應(yīng)用中,根據(jù)系統(tǒng)的要求,要存儲的數(shù)據(jù)量為每間隔5 ms 存儲256 個字節(jié),可計(jì)算得到存儲的數(shù)據(jù)量為51 kbit/s,則存滿1 頁需要40 ms,存滿1 塊需要2.56 s,存滿1 個分區(qū)需要約38 min, 即大約每隔38 min 就要對塊1 進(jìn)行1 次寫操作。根據(jù)NANDFlash 壽命按10 萬次寫操作計(jì)算[7],則NAND Flash 塊1 在本系統(tǒng)中的使用時長約為6.3 萬h,能夠滿足正常的使用需求。

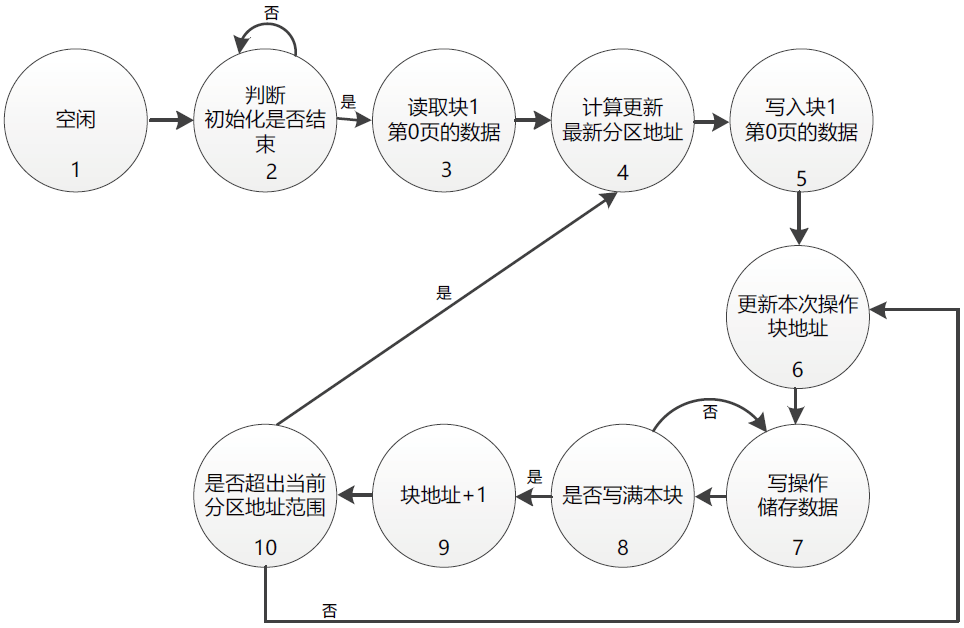

2.1.4 分區(qū)狀態(tài)機(jī)的設(shè)計(jì)

根據(jù)分區(qū)機(jī)理,FPGA 的工作控制模塊設(shè)計(jì)了分區(qū)相關(guān)的狀態(tài)機(jī),狀態(tài)機(jī)流程如圖5 所示,狀態(tài)跳轉(zhuǎn)如下:上電后,狀態(tài)機(jī)從狀態(tài)1 跳轉(zhuǎn)至狀態(tài)2,判斷初始化是否結(jié)束。等待初始化結(jié)束后,狀態(tài)機(jī)跳轉(zhuǎn)至狀態(tài)3,讀取塊1的第0 頁中的數(shù)據(jù),得到上一次的分區(qū)信息;在狀態(tài)4 中計(jì)算中更新本次要操作的最新的分區(qū)地址。狀態(tài)機(jī)依次跳轉(zhuǎn)至狀態(tài)5、6,將更新后的最新分區(qū)地址寫入塊1 的第0 頁,且更新本次操作的塊地址。狀態(tài)機(jī)跳轉(zhuǎn)至狀態(tài)6,進(jìn)行正常的數(shù)據(jù)存儲操作。狀態(tài)7、8,9 為正常的連續(xù)寫操作狀態(tài)。狀態(tài)10 時判斷是否超出本分區(qū),如果超出,則跳轉(zhuǎn)至狀態(tài)4 重新計(jì)算并更新分區(qū)地址,否則跳轉(zhuǎn)至狀態(tài)6 繼續(xù)存儲數(shù)據(jù)。

圖5 狀態(tài)機(jī)轉(zhuǎn)換圖

當(dāng)電路下電,再次上電后,狀態(tài)機(jī)會跳過上一次操作的分區(qū),從下一分區(qū)開始存儲數(shù)據(jù),保證了數(shù)據(jù)存儲的連續(xù)性,前一次的存儲的數(shù)據(jù)不會被本次數(shù)據(jù)覆蓋,本次數(shù)據(jù)前一次操作的分區(qū)的下一分區(qū)進(jìn)行存儲。

3 驗(yàn)證情況

驗(yàn)證的電路框圖如圖6 所示。在NAND Flash控制器中進(jìn)行驗(yàn)證,分區(qū)功能嵌入在工作控制模塊中,在FPGA 中設(shè)計(jì)1 個模擬數(shù)據(jù)源,模擬系統(tǒng)發(fā)送的數(shù)據(jù),每隔5 ms 寫入256 個字節(jié)數(shù)據(jù);通過維護(hù)串口與上位機(jī)進(jìn)行通信,可以通過上位機(jī)啟動控制器工作和停止,讀取塊1 的數(shù)據(jù)等[8]。

圖6 壞塊表模塊驗(yàn)證電路框圖

驗(yàn)證內(nèi)容分為兩部分,首先為不跨分區(qū)的自動續(xù)存功能驗(yàn)證,其次為跨分區(qū)的自動續(xù)存功能驗(yàn)證。

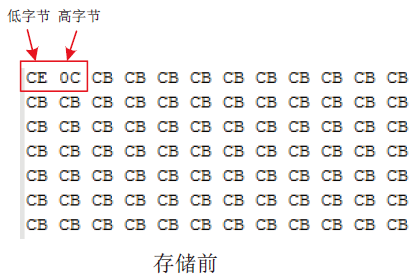

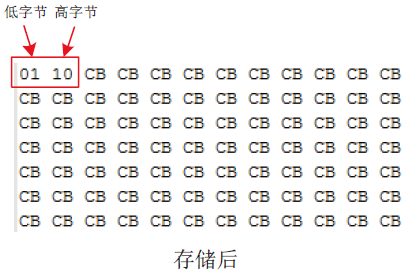

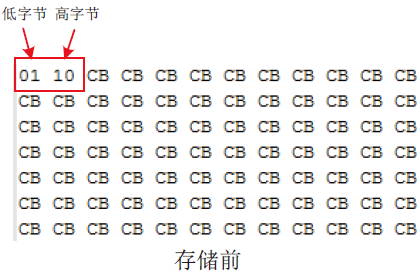

不跨分區(qū)驗(yàn)證時,驗(yàn)證的存儲時長約為1 min。先通過維護(hù)串口與上位機(jī)發(fā)送讀取命令,先讀取塊1 的數(shù)據(jù),得到本次存儲前的最新分區(qū)信息,然后發(fā)送存儲命令,1 分鐘后直接下電重啟,再次讀取塊1 的數(shù)據(jù),對比第2 次讀到的最新分區(qū)信息,如圖7 所示。存儲前分區(qū)信息為0×0CCE,即分區(qū)4。存儲后分區(qū)信息為0×1001,即分區(qū)5。說明本次存儲的數(shù)據(jù)在分區(qū)5,成功跳過了分區(qū)4,分區(qū)4 為上一次存儲的空間。

圖7 不跨分區(qū)試驗(yàn)結(jié)果

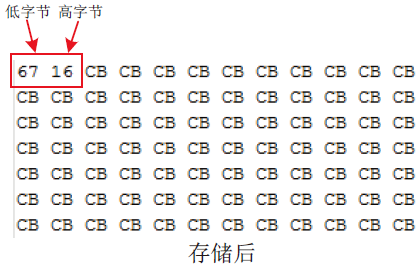

跨分區(qū)驗(yàn)證的存儲時長約為45 min,大于38 min,以確保存儲的數(shù)據(jù)能夠超過1 個分區(qū)。先通過上位機(jī)發(fā)送讀取命令,先讀取塊1 的數(shù)據(jù),得到本次存儲前的最新分區(qū)信息,然后發(fā)送存儲命令,45 分鐘后下電重啟,再次讀取塊1 的數(shù)據(jù),對比第2 次讀到的最新分區(qū)信息,如圖8 所示。存儲前分區(qū)信息為0×1001,即分區(qū)5。存儲后分區(qū)信息為0×1667,即分區(qū)7。說明本次存儲的數(shù)據(jù)在分區(qū)6 和分區(qū)7,成功實(shí)現(xiàn)了跨過分區(qū)的存儲和更新了最新分區(qū)地址信息。

圖8 跨分區(qū)試驗(yàn)結(jié)果

綜上,通過實(shí)驗(yàn)證明,本文設(shè)計(jì)的基于FPGA 的自動分區(qū)續(xù)存功能夠正確地實(shí)現(xiàn),方法簡單便捷,滿足系統(tǒng)對NAND Flash 存儲器芯片的多次存儲的控制需求。

4 結(jié)束語

本文提出了一種基于FPGA 的自動分區(qū)續(xù)存功能的方法,該方法簡單方便的實(shí)現(xiàn)了存儲器的分區(qū)管理,滿足了數(shù)據(jù)分區(qū)續(xù)存的需求,并得到了試驗(yàn)證明。該方法的分區(qū)續(xù)存功能準(zhǔn)確可靠,目前已經(jīng)在實(shí)際產(chǎn)品中得到了應(yīng)用和驗(yàn)證。

參考文獻(xiàn):

[1] 賈鑫,張少平.基于貪婪策略的NAND Flash存儲器的磨損均衡算法研究[J].計(jì)算機(jī)科學(xué),2017,44(11).

[2] 劉俊.基于FPGA的FLASH控制器設(shè)計(jì)[J].電子技術(shù)與軟件工程,2016,23(11).

[3] 任勇峰,周濤.基于Flash的侵徹關(guān)鍵信號分區(qū)存儲方法[J].探測與控制學(xué)報(bào),2015,37(5).

[4] 李遠(yuǎn)哲,賀海文.嵌入式系統(tǒng)大容量NANDFlash存儲器分區(qū)管理設(shè)計(jì)[J].計(jì)算機(jī)測量與控制,2019,2.

[5] 濮建福, 李世健.延長E E PROM使用壽命的均勻磨損算法[J].電子設(shè)計(jì)工程,2016,24(8).

[6] 鄒姍蓉,李杰.基于FPGA的智能分區(qū)存儲系統(tǒng)設(shè)計(jì)[J].電子器件,2016,39(6).

[7] 張卓,任家峪.一種基于NAND Flash基帶數(shù)據(jù)模擬源的設(shè)計(jì)與實(shí)現(xiàn)[J].太赫茲科學(xué)與電子信息學(xué)報(bào),2016,14(5).

[8] 張子明, 吳海建, 等. 基于F P G A的閃存XX29F系列讀寫裝置的設(shè)計(jì)[J].測控技術(shù),2016,35(7).

(本文來源于《電子產(chǎn)品世界》雜志2023年8月期)

評論