長電科技 XDFOI Chiplet 系列工藝實現穩定量產

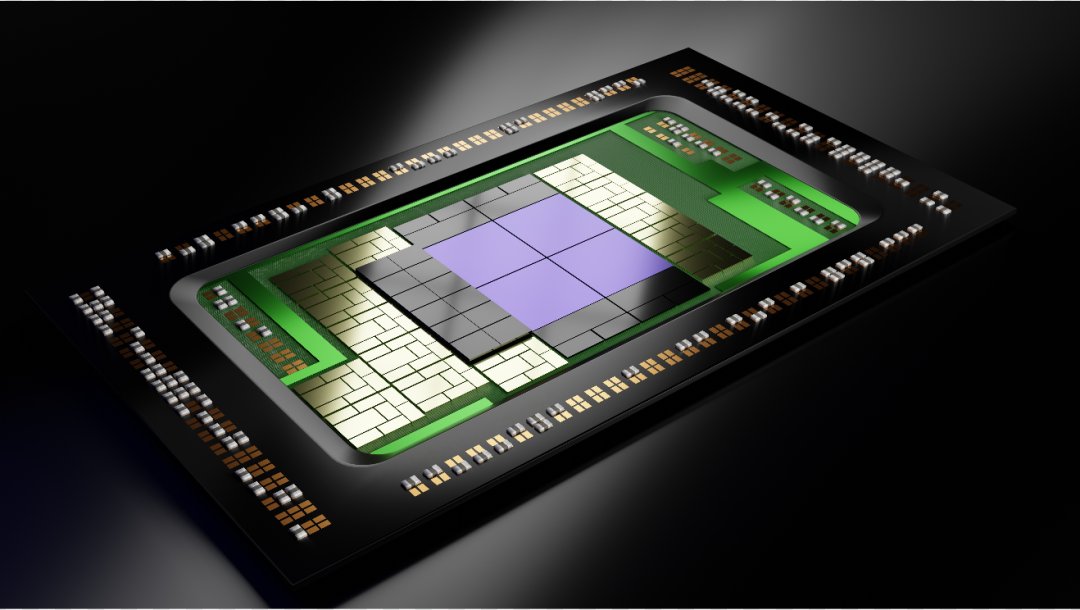

IT之家 1 月 5 日消息,長電科技宣布,公司 XDFOI Chiplet 高密度多維異構集成系列工藝已按計劃進入穩定量產階段,同步實現國際客戶 4nm 節點多芯片系統集成封裝產品出貨,最大封裝體面積約為 1500mm2 的系統級封裝。

本文引用地址:http://www.104case.com/article/202301/442394.htm長電科技于 2021 年 7 月推出了面向 Chiplet(小芯片)的高密度多維異構集成技術平臺 XDFOI,利用協同設計理念實現了芯片成品集成與測試一體化,涵蓋 2D、2.5D、3D Chiplet 集成技術。

長電科技 XDFOI 通過小芯片異構集成技術,在有機重布線堆疊中介層(RDL Stack Interposer,RSI)上,放置一顆或多顆邏輯芯片(CPU / GPU 等),以及 I / O Chiplet 和 / 或高帶寬內存芯片(HBM)等,形成一顆高集成度的異構封裝體。一方面可將高密度 fcBGA 基板進行“瘦身”,將部分布線層轉移至有機重布線堆疊中介層基板上,利用有機重布線堆疊中介層最小線寬線距 2μm 及多層再布線的優勢,縮小芯片互連間距,實現更加高效、更為靈活的系統集成;另一方面,也可將部分 SoC 上互連轉移到有機重布線堆疊中介層,從而得以實現以 Chiplet 為基礎的架構創新,而最終達到性能和成本的雙重優勢。

IT之家了解到,長電科技 XDFOI 技術可將有機重布線堆疊中介層厚度控制在 50μm 以內,微凸點(μBump)中心距為 40μm,實現在更薄和更小單位面積內進行高密度的各種工藝集成,達到更高集成度、更強模塊功能和更小封裝尺寸。同時,還可以在封裝體背面進行金屬沉積,在有效提高散熱效率的同時,根據設計需要增強封裝的電磁屏蔽能力,提升芯片成品良率。

長電科技 XDFOI Chiplet 高密度多維異構集成系列工藝已在高性能計算、人工智能、5G、汽車電子等領域應用。

評論