超結(jié)結(jié)構(gòu)的功率MOSFET輸出電容特性

1 超結(jié)結(jié)構(gòu)的高壓功率MOSFET

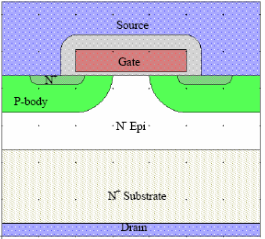

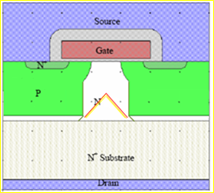

功率MOSFET的輸出電容Coss會隨著外加電壓VDS的變化而變化,表現(xiàn)出非線性的特性,超結(jié)結(jié)構(gòu)的高壓功率MOSFET采用橫向電場的電荷平衡技術(shù),如圖1所示。相對于傳統(tǒng)的平面結(jié)構(gòu),超結(jié)結(jié)構(gòu)將P型體區(qū)下沉,這樣在其內(nèi)部形成P柱,和N區(qū)非常寬的接觸面產(chǎn)生寬的耗盡層,也就是空間電荷區(qū),空間電荷區(qū)形成的電場,也就是橫向電場,保證器件的耐壓;同時,原來N區(qū)漂移層就可以提高摻雜濃度,降低導(dǎo)通電阻。和標(biāo)準(zhǔn)MOSFET相比,橫向電場電荷平衡技術(shù)可以極大的減小硅片尺寸,得到更低的RDSON和更低的電容。[2-4]

8月刊,四川大學(xué)計算機學(xué)院,萬國半導(dǎo)體元件(深圳)有限公司應(yīng)用中心

(a) 平面結(jié)構(gòu)

(b) 超結(jié)結(jié)構(gòu)

圖1 平面結(jié)構(gòu)和超結(jié)結(jié)構(gòu)的高壓功率MOSFET

2 超結(jié)結(jié)構(gòu)的高壓功率MOSFET寄生電容形成

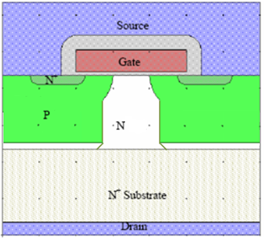

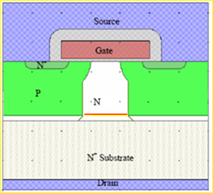

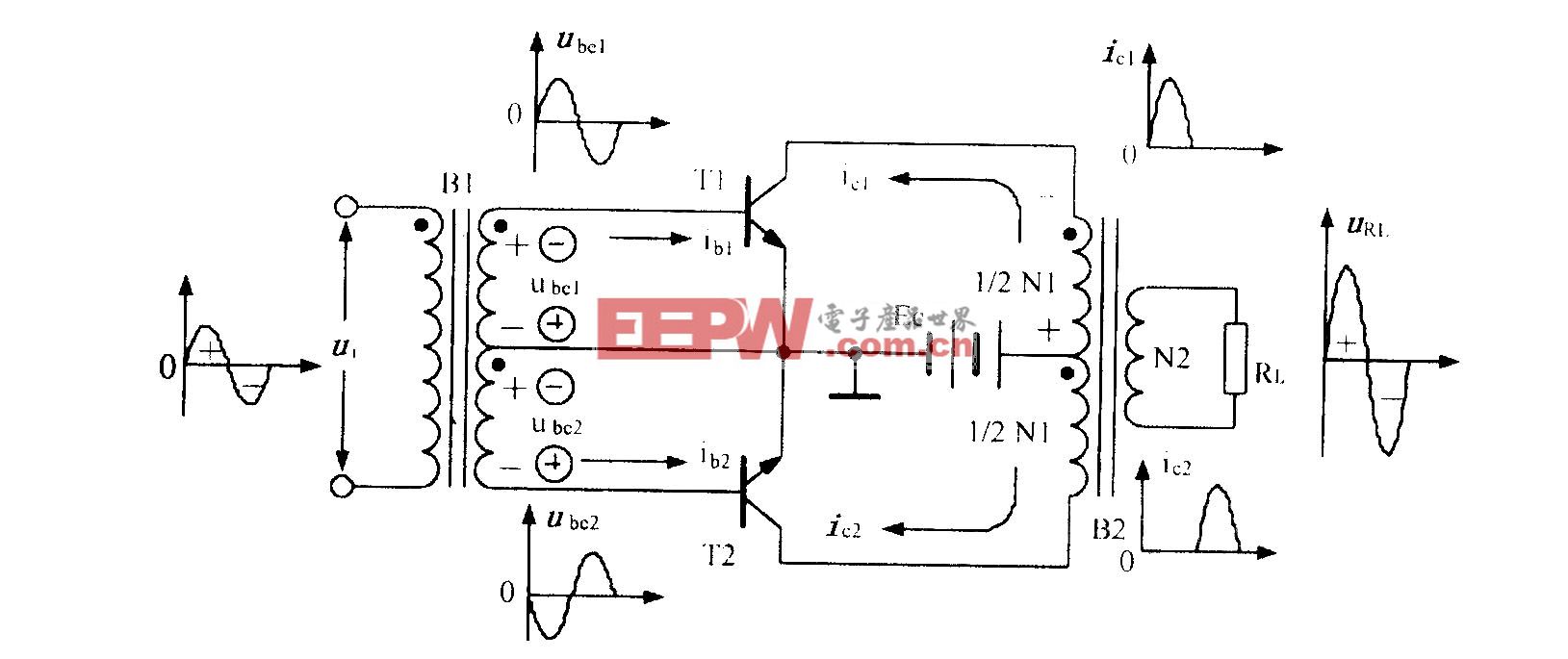

超結(jié)結(jié)構(gòu)的功率MOSFET在VDS電壓上升、橫向電場建立產(chǎn)生耗盡層(空間電荷區(qū))過程中,N型漂移層兩側(cè)的空間電荷區(qū)邊界會向中心移動,如圖2所示,隨著VDS電壓的升高,兩側(cè)空間電荷區(qū)邊界會接觸碰到一起,然后向再下繼續(xù)移動。在這個過程中,直接影響輸出電容Coss和反向傳輸電容Crss的主要參數(shù)有:漏極和源極、柵極和漏極相對的面積、形狀、厚度,以及相應(yīng)的空間電荷區(qū)相對的距離。

(a) VDS電壓非常低

(b) VDS增加到電容突變電壓

(c) VDS處于電容突變電壓區(qū)

(d) VDS達到最大值

圖2 空間電荷區(qū)建立過程

VDS電壓低時,P柱結(jié)構(gòu)周邊的空間電荷區(qū)厚度相對較小,而且空間電荷區(qū)沿著P柱的截面發(fā)生轉(zhuǎn)折,相對的有效面積很大,如圖2(a)所示,因此輸出電容Coss和反向傳輸電容Crss的電容值非常大;VDS電壓提高,空間電荷區(qū)沿著P柱的截面發(fā)生下移,當(dāng)VDS電壓提高到某一個區(qū)間,兩側(cè)的空間電荷區(qū)相互接觸時,同時整體下移,電容的有效面積急劇降低, 同時空間電荷區(qū)厚度也急劇增加,因此Coss和Crss電容在這個VDS電壓區(qū)間也隨之發(fā)生相應(yīng)的突變,產(chǎn)生非常強烈的非線性特性,如圖2(b) 和(c)所示;VDS電壓提高到更高的值,整個N區(qū)全部耗盡變?yōu)榭臻g電荷區(qū)空間,此時電容的有效面積降低到非常、非常小的最低時,如圖2(d)所示,輸出電容Coss也降低到非常、非常小的最低值。

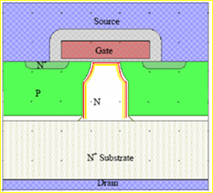

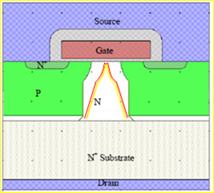

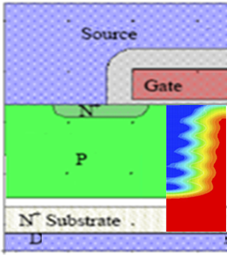

在低電壓時,相對于柱結(jié)構(gòu)和單元尺寸,空間電荷區(qū)厚度相對較小,P柱結(jié)構(gòu)周邊,空間電荷區(qū)發(fā)生轉(zhuǎn)折,導(dǎo)致輸出電容的有效面積變大。這2種因素導(dǎo)致在低壓時,Coss的值較大。VDS電壓升高時,如VDS=20 V,VDS=100 V,從圖3空間電荷區(qū)電場分布仿真圖可以看到,

空間電荷區(qū)的形狀開始變化,首先沿著補償?shù)慕Y(jié)構(gòu)經(jīng)過波浪形的,然后進入更低有效面積的水平電容,因此高壓的輸出電容降低到2個數(shù)量級以下。

Crss和Coss相似,電容曲線的突變正好發(fā)生在上面二種狀態(tài)過渡的轉(zhuǎn)變的過程。

(a) 20 V空間電荷區(qū)電場分布

(b) 100 V空間電荷區(qū)電場分布

圖3 空間電荷區(qū)電場分布

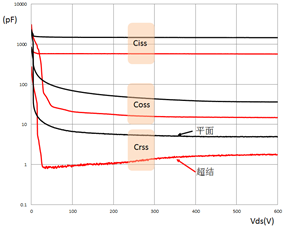

圖4展示了平面和超結(jié)結(jié)構(gòu)高壓功率MOSFET的電容曲線,從圖中的曲線可以的看到,當(dāng)偏置電壓VDS從0變化到高壓時,輸入電容Ciss沒有很大的變化, Coss 和 Crss 在低壓的時候非常大,在高壓時變得非常小。在20~40 V的區(qū)間,產(chǎn)生急劇、非常大的變化。

圖4 平面和超結(jié)結(jié)構(gòu)高壓功率MOSFET的電容

3 工藝對超結(jié)結(jié)構(gòu)的高壓功率MOSFET寄生電容影響

新一代超結(jié)技術(shù)進一步降低內(nèi)部每個晶胞單元尺寸,對于同樣的導(dǎo)通電阻,降低內(nèi)部晶胞單元尺寸可以降低硅片的尺寸,從而進一步硅片的尺寸以及相關(guān)的寄生電容,器件就可以工作在更高頻率,采用更小的封裝尺寸,降低系統(tǒng)的成本。

內(nèi)部的晶胞單元尺寸采用更小的尺寸,在更小的硅片面積實現(xiàn)以前的技術(shù)相同的或者更低的導(dǎo)通電阻,就必須要求漂移層N區(qū)電流路徑的摻雜濃度更高,內(nèi)部會產(chǎn)生更高的橫向電場也就是更強烈的電荷平衡特性,保證內(nèi)部空間電荷區(qū)獲得所要求的擊穿電壓;同時,內(nèi)部結(jié)構(gòu)中每個柱狀結(jié)構(gòu)的高度對寬度的比值增加,上述的這些因素導(dǎo)致新一代技術(shù)的超結(jié)結(jié)構(gòu)的高壓功率MOSFET的Coss和Crss的電容曲線的突變電壓區(qū)將降低到更低的電壓,寄生電容的非線性特性更為劇烈。

不同的工藝,轉(zhuǎn)折點的電壓不一樣,轉(zhuǎn)折點的電壓越低,電容的非線性特性越強烈,對功率MOSFET的開關(guān)特性以及對系統(tǒng)的EMI影響也越強烈。采用以前技術(shù)的超結(jié)結(jié)構(gòu)的輸出電容Coss非線性特性的VDS電壓區(qū)間為40-60V,新一代的超結(jié)結(jié)構(gòu)的輸出電容Coss非線性特性的VDS電壓區(qū)間為20~30 V。電容Crss和電容Coss的下降發(fā)生在更低的電壓區(qū)間,這種效應(yīng)在開關(guān)過程形成更快的開關(guān)速度,可以明顯的降低開關(guān)損耗。Crss小,減小開關(guān)過程中電流和電壓的交越時間。

另外,因為功率MOSFET在關(guān)斷過程中,儲存在輸出電容Coss能量將會在每一個開關(guān)周期開通的過程中消耗在溝道中,新一代超結(jié)結(jié)構(gòu)的功率MOSFET在高壓時輸出電容Coss降低得更低,Coss下降突變發(fā)生在更低的電壓區(qū),儲存在輸出電容Coss的能量Eoss等于輸出電容對VDS電壓在工作電壓范圍內(nèi)的積分計算得到,因此,Eoss能量降低到更低的值,進一步的降低硬開關(guān)工作過程中的開關(guān)損耗,特別是在輕載的時候,Eoss產(chǎn)生的開關(guān)損耗的作用更加明顯,可以極大提高系統(tǒng)輕載的效率。[1] [5]

然而,Coss和Crss這種效應(yīng)在開關(guān)過程中,VDS電壓經(jīng)過這個電壓區(qū)間,將會產(chǎn)生非常大的du/dt和di/dt,容易在驅(qū)動的柵極和漏極產(chǎn)生電壓振蕩,形成過高的VGS、VDS過電壓尖峰,同時對系統(tǒng)EMI產(chǎn)生影響。

4 結(jié)論

1)超結(jié)結(jié)構(gòu)的功率MOSFET內(nèi)部P柱形成耗盡層及橫向電場過程中,耗盡層空間電荷區(qū)的形狀改變,導(dǎo)致影響輸出電容的極板面積和距離發(fā)生劇烈的改變,輸出電容具有強烈的非線性特性。

2)新一代超結(jié)技術(shù)采用更小晶胞單元尺寸,導(dǎo)致輸出電容轉(zhuǎn)折點電壓進一步降低,對應(yīng)的開關(guān)損耗減低,同時輸出電容非線性特性進一步加劇。

3)輸出電容非線性特性產(chǎn)生非常大的du/dt和di/dt,對系統(tǒng)EMI產(chǎn)生影響。

參考文獻:

[1] 劉松. 理解功率MOSFET的開關(guān)損耗[J].今日電子,2009(10):52-55.

[2] 劉松.超結(jié)型高壓功率MOSFET結(jié)構(gòu)工作原理[J].今日電子, 2013(11):30-31.

[3] 劉松.功率MOSFET應(yīng)用問題分析提高篇[J].今日電子, 2015(2): 30-33.

[4] 劉松.功率MOSFET應(yīng)用問題分析基礎(chǔ)篇[J].今日電子, 2014(12): 43-46.

[5] 劉松.理解MOSFET時間相關(guān)及能量相關(guān)輸出電容Coss(tr)和Coss(er)[J].電子產(chǎn)品世界, 2019(4):62-65.

作者簡介:

劉松,男,碩士,總監(jiān),主要從事開關(guān)電源系統(tǒng)、電力電子系統(tǒng)和模擬電路的應(yīng)用研究和開發(fā)工作。獲廣東省科技進步二等獎一項,發(fā)表技術(shù)論文60多篇。

(本文來源于《電子產(chǎn)品世界》雜志2020年8月期)

評論