基于CPRI協議的5G高速光纖接口研究

李奧,徐蘭天

本文引用地址:http://www.104case.com/article/201907/402133.htm(中國電子科技集團公司第四十一研究所,安徽 蚌埠 233010)

摘要:“高速率”是5G通信的主要特性之一,為滿足即將到來的5G高速數據傳輸需求,需要提供一種高速穩定的數據傳輸接口。本文就光纖傳輸結合支持多級傳輸速率的CPRI協議,設計出一種高速光纖接口控制板,控制板采用高性能的Virtex-6系列FPGA作為主要控制芯片,經過仿真驗證,該控制板支持近10Gbit/s速率數據的穩定傳輸,具備高速的通信傳輸能力,完全支持5G通信的高速率傳輸。高速光纖接口控制板可用于多種5G設備的研究與開發,在5G開發行業與其它高速率數據傳輸場景具有很好的應用價值。

*項目基金:中國電科技術創新基金項目《微波毫米波大帶寬大規模MIMO測試技術研究》

0 引言

新一代移動通信技術5G通信正在如火如荼的推進當中,5G相比4G帶來了數據流量和傳輸速率的大幅度提升,其典型用戶數據速率將提升10~100倍,峰值速率可達10 Gbit/s [1] 。高速的數據傳輸速率給傳統的雙絞線傳輸介質帶來了巨大壓力,而光纖通信具有傳輸速度快、損耗低、容量大等特點, 非常適用于高速數據傳輸,不過光纖接口相比于傳統網絡傳輸介質的接口也更為復雜。由愛立信,華為,NEC,西門子和北電組成的通用無線接口聯盟規定了CPRI協議標準,CPRI作為通用公共無線接口提供了無線控制設備(REC)與無線設備(RE)之間的通信標準,通用的開放標準極大節約了產品成本,提高了其通用性和靈活性,有效地解決了5G通信下數據的高速傳輸需求。因此,基于CPRI協議的高速光纖接口研究具有重要的價值與意義。

本文采用Xilinx公司的Virtex6系列芯片與高性能DSP處理器相結合,設計出可控制4個光口收發的控制板。可采用回環測試方法對光口收發狀態進行測試,構成一套可實現多級速率、數據收發狀態實時分析的高速光纖接口板卡。

2 CPRI協議概述

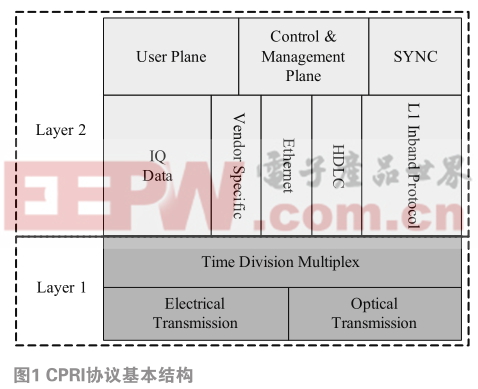

CPRI協議定義了物理層(Layer 1)和數據鏈路層(Layer 2),其中物理層包括電學傳輸接口和光學傳輸接口,數據鏈路層支持同向和正交數據、廠商特定信息、以太網、高級數據鏈路控制以及L1帶內協議 [2] ,其基本結構如圖1所示。

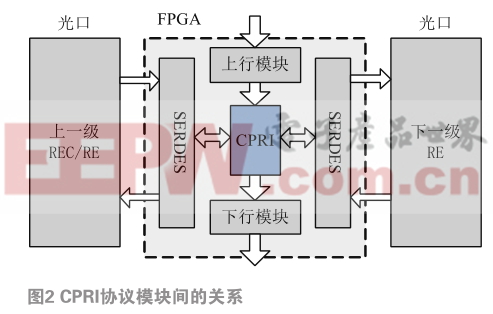

CPRI協議支持從614 Mbps到9830 Mbps的多級速率等級,目前市場上的專用高速接口芯片很少能夠支持CPRI的9830 Mbps速率等級,而支持該速率等級的FPGA型號較多,故本文選用性價比較高的Virtex6系列FPGA芯片。CPRI協議能夠有效處理REC與RE或RE與RE之間的光纖連接,其可將數條并行CPRI數據鏈路進行串行化處理,從而實現光纖的超高速傳輸,CPRI協議模塊間的關系如圖2所示。

3 高速光口控制板設計

3.1 硬件架構設計

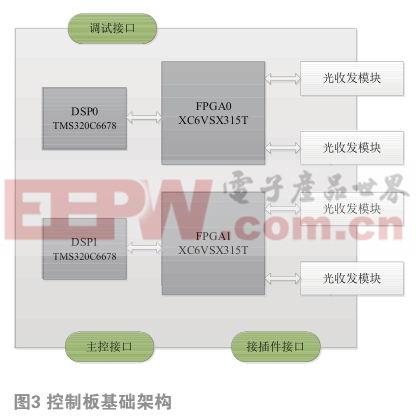

本文所要研究的高速光纖接口基于Virtex6系列FPGA芯片與高性能DSP處理器所設計的控制板,光口傳輸速率高達10Gb/s。控制板能通過預留的主控接口與上位機之間通信,并通過DSP來控制數據的收發, FPGA來控制光口的通信以及數據的整理功能,整個控制板的基本架構如圖3所示。

控制板包含四個光收發模塊,分別由一個DSP和一個FPGA控制兩個光收發模塊,DSP具有較高的工作頻率,其內部集成了網絡MAC接口,外接一個物理層芯片就可以實現高達千兆的網絡通信。本文介紹的控制板基于多核數字信號處理器TMS320C6678,可實現單個芯片連接兩個千兆網口,這兩個網口可以各自獨立傳輸數據,也可以聯合傳輸數據,提高了實際的數據傳輸速率。FPGA與DSP之間可通過FIFO進行速率匹配,本文中控制板選用Xilinx公司型號為XC6VSX315T的FPGA作為主控芯片用來控制光纖接口的主要功能,主要功能是完成光收發模塊的使能控制、光傳輸的鏈路管理以及數據傳輸的控制,同時XC6VSX315T包含豐富的Slices及多個用戶I/O,可以滿足控制板的電路設計要求和后期擴展與增強功能的設計,XC6VSX315T還包含5組GTX數據收發接口,每組GTX通道的傳輸速率最快可達6.6 Gb/s,可以滿足光纖接口的高速率要求 [3] 。此外,控制板還設計了主控接口,用于實現與上位機之間的通信,設計調試接口用于控制與調試,設計接插件接口用于外接其它接插件,很好的提高了其靈活性與可擴展性。

整個控制板基于VPX架構,主體芯片除兩片DSP及兩片Virtex-6 FPGA外,還包括1個RapidIO Switch。每片FPGA通過EMIF總線連接一片DSP,預留的調試接口可插接FMC子卡,FPGA可連接FMC子卡進行調試。FPGA芯片外掛接2簇32 bit DDRIII SDRAM,最大容量支持2 GB。FPGA與DSP進行的所有信號處理均通過SRIO連接板上一片8端口SRIO交換芯片。DSP芯片外掛最大容量支持2 GB的DDRIII SDRAM。兩片DSP之間通過HyperLink進行高速直接互聯。兩片FPGA之間通過GTX以及若干LVDS信號互聯。控制板設計符合工業級要求,其主體芯片架構如下圖所示。

3.2 軟件架構設計

高速光纖接口控制板由FPGA作為主控芯片來控制光纖接口的主要功能,本次設計采用FPGA與CPRI的結合來實現光口的多級速率,控制工程采用Verilog硬件描述語言來作為設計語言,Verilog語言因其簡單易讀,穩定可靠等優越性逐漸發展成為目前使用最為廣泛的硬件描述語言。使用Verilog描述硬件的基本設計單元是模塊,通過模塊的相互連接調用來實現復雜的電子電路,模塊中可以包括組合邏輯部分的邏輯電路圖、邏輯表達式、邏輯系統所完成的邏輯功能以及過程時序部分 [4] 。本文使用Xilinx Vivado 2017.2集成開發環境來實現高速光纖接口控制板的功能設計。

本文采用標準的FPGA的邏輯設計的基本方式,模塊化相應的功能,根據功能進行模塊劃分可分為時鐘管理模塊、數據控制與監測模塊和CPRI IP核的調用模塊三個模塊,另外還有頂層模塊負責調用各子模塊以及數據接口。

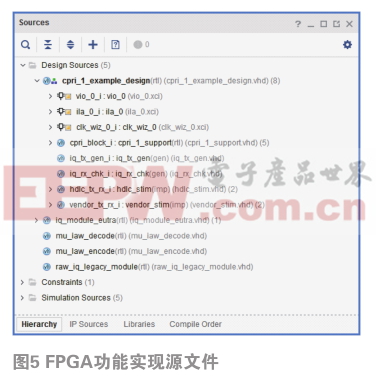

控制板的主控芯片主要實現部分有:頂層模塊(cpri_1_example_design),全局時鐘管理模塊(clk_wiz_0_i: clk_wiz_0),數據監測模塊(ila_0_i: ila_0),光口數據控制與產生模塊(iq_tx_gen_i: iq_tx_gen),光口數據接收模塊(iq_rx_clk_i: iq_rx_chk),以及工程約束文件(cpri_1_example_design.xdc)等。

FPGA內部CPRI在發送端完成8 B/10 B編碼和并串轉換,在接收端完成8 B/10 B解碼和串并轉換。通過調用監測模塊設置的監測腳可以觀測時鐘狀態及光口數據的收發狀態。發送模塊中,CPRI的標準16位數據拆分為高8位和低8位,使用FPGA的DDR模塊將兩部分數據拼接成DDR數據發送出去;接收模塊將收到的DDR數據并行傳輸給FPGA,經過同步與拼接后得到16位的CPRI數據,最后數據傳給CPRI模塊來進行解幀處理。

本次的光口數據傳輸過程中使用的CPRI協議已經驗證是穩定可靠的傳輸協議,并封裝成可直接調用的IP核,該協議核內部封裝了高速串行數據接口硬核,可編程邏輯器件通過綁定GTX通道進行數據的收發交互。單個GTX通道的數據傳輸速率可實現多個速率級別,最高可達將近10 Gbit/s,根據不同的需求可以多個通道的組合使用,從而可實現幾十Gbit速率甚至上百Gbit速率的數據傳輸,在實驗測試中,所調用的CPRI核可以方便的設置多個等級的CPRI線性速率,從而可以很好的研究光口在不同速率下的收發狀態 [5] ,下圖所示為可調用的CPRI協議的IP核界面。

4 高速光纖接口測試

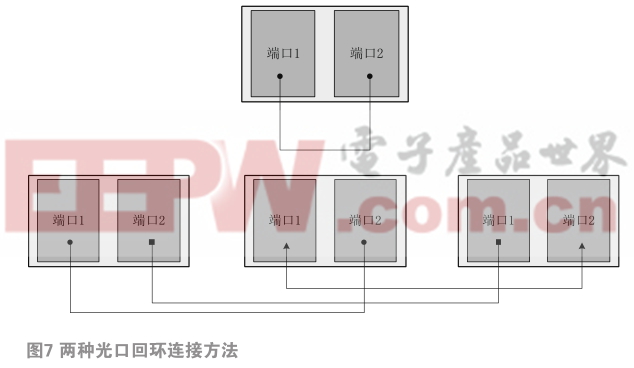

本文采用光口回環測試方法對高速光纖通信系統進行測試,使用光模塊和光纖線纜將一個或多個光收發模塊構成回環,通過數據監測模塊設置的監測腳觀測光口的收發狀態進行分析。SFP+光收發一體模塊包含兩個光纖接入端口,分別可用作發射端口與接收端口,并且體積小、易插拔,能夠很好的滿足本文的測試要求。為提高測試精度及測試效率,本文分別采用單光口自回環連接方式及三個光口構成回環連接方式進行測試,連接方法如下圖所示。

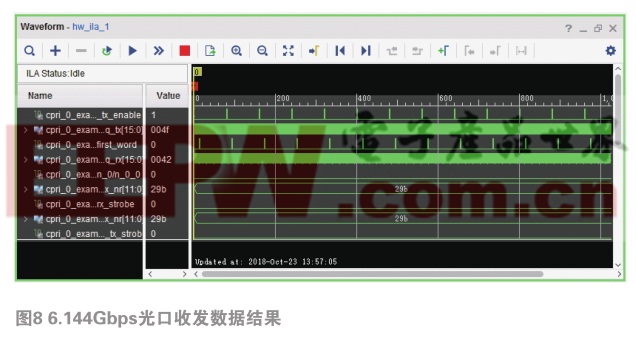

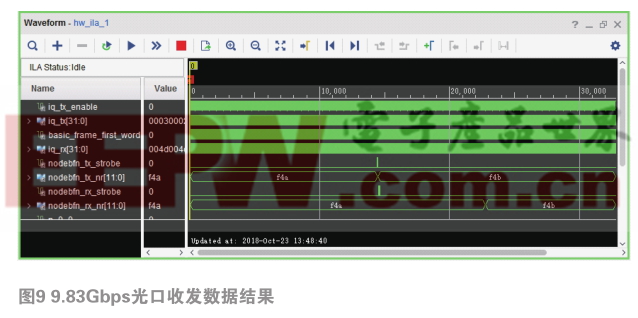

為了驗證光纖通信系統能否滿足5G通信的高速率傳輸要求以及數據傳輸的可靠性,本文分別就6.144 Gbps和9.83 Gbps兩個CPRI速率等級進行了測試。首先在測試文件中定義了一個數據產生模塊,發送端產生的測試數據通過光模塊端口輸出,經過光纖回環到另一個光模塊端口。數據監測模塊定義了發射端監測腳和接收端監測腳分別用來監測發射端口與接收端口的數據狀態。在6.144 Gbit/s速率下,定義16位數據監測腳,在9.83Gbps速率下定義32位數據監測腳。

采用Vivado 2017.2軟件中的BehavioralSimulation進行仿真驗證,經驗證,兩種速率等級下光纖通信系統均能正常收發數據,并且滿足5G通信的基本指標。

5 結論

本文為滿足5G高速通信需求,設計了一種基于CPRI協議的高速光纖接口控制板,該控制板具有高性能的數據處理能力和高速的傳輸通信能力。通過在6.144 Gbps和9.83 Gbps兩個速率等級下的測試驗證,高速光纖接口控制板具有較好的穩定性與可靠性,并且滿足5G通信的基本指標。該高速光纖接口控制板可用于5G信號發生器與5G信號測試裝置等設備的研究和開發,對5G通信技術的發展與普及具有重大意義。

參考文獻:

[1]屠方澤.5G面臨的測試挑戰及解決方案[J].電子產品世界,2017(5): 18-19.

[2]馬志剛.CPRI原理及測試解決方案 [J].電信網技術,2010(5): 68-70.

[3]Xilinx.Virtex-6 Family Overview [Z].America: Xilinx Inc,2015.

[4]胡澤文.基于CPRI協議的光纖通訊設計與實現 [J].電子元器件應用,2011(2): 27-30.

[5]章潔.基于FPGA的高速光纖通信IP核研究設計[J].數字技術與應用,2015(5): 29-30.

作者簡介:

李奧(1993-),男,助理工程師,主要研究方向:信號與信息處理

本文來源于科技期刊《電子產品世界》2019年第7期第36頁,歡迎您寫論文時引用,并注明出處

評論