宜特晶背FIB電路修補能力突破7奈米工藝

隨半導體產業朝更先進工藝 發展之際,宜特電路修補技術(IC Circuit Edit)檢測技術再突破!宜特今(3/15)宣布,宜特通過先進工藝 客戶肯定,IC芯片背面(Backside,簡稱晶背)FIB電路修補技術達7奈米(nm)工藝 。

本文引用地址:http://www.104case.com/article/201903/398547.htm宜特針對IC設計業者為何須進行電路修補進行說明。由于即使電路仿真軟件不斷地提升演進,仍難以100%來確保芯片的設計及布局正確性,一旦發現電路瑕疵只能再次進行光罩改版;然而光罩價格不斐,且重新下光罩后,等待修補過后的芯片時間通常超過一個月。因此,多數IC設計業者,會選擇進行IC電路修補,只需幾個小時內即可完成修補,確保電路設計符合預期,并降低時間及金錢的成本耗損。

宜特表示,隨著摩爾定律,半導體工藝 從1微米(um)、0.5微米(um)、0.13微米(um)不斷微縮到奈米(nm)等級,如此先進工藝 的電路修補,考驗FIB實驗室的技術發展及應用能力。特別當工藝 來到16奈米(nm)以下的工藝 ,包裝型式多數為覆晶技術(Flip Chip),因此FIB電路修補就必須從晶背來執行,整體困難度也隨之增加。

宜特進一步指出,7奈米(nm)先進工藝 的晶背電路修補,有兩個挑戰。第一,晶體管密度倍增:每平方毫米密度約是16nm工藝 的3.5倍,要穿越遍布于底層的晶體管進行修補困難度將大幅度提升;第二,薄且小的間隙:7奈米(nm)工藝 的金屬與介電層的間隙、寬度、厚度,多為40奈米(nm)或以下,面對薄且小的工藝 ,如何精準定位目標、清楚辨識電路及避免過度曝露金屬,更是修補技術能力重要關鍵。

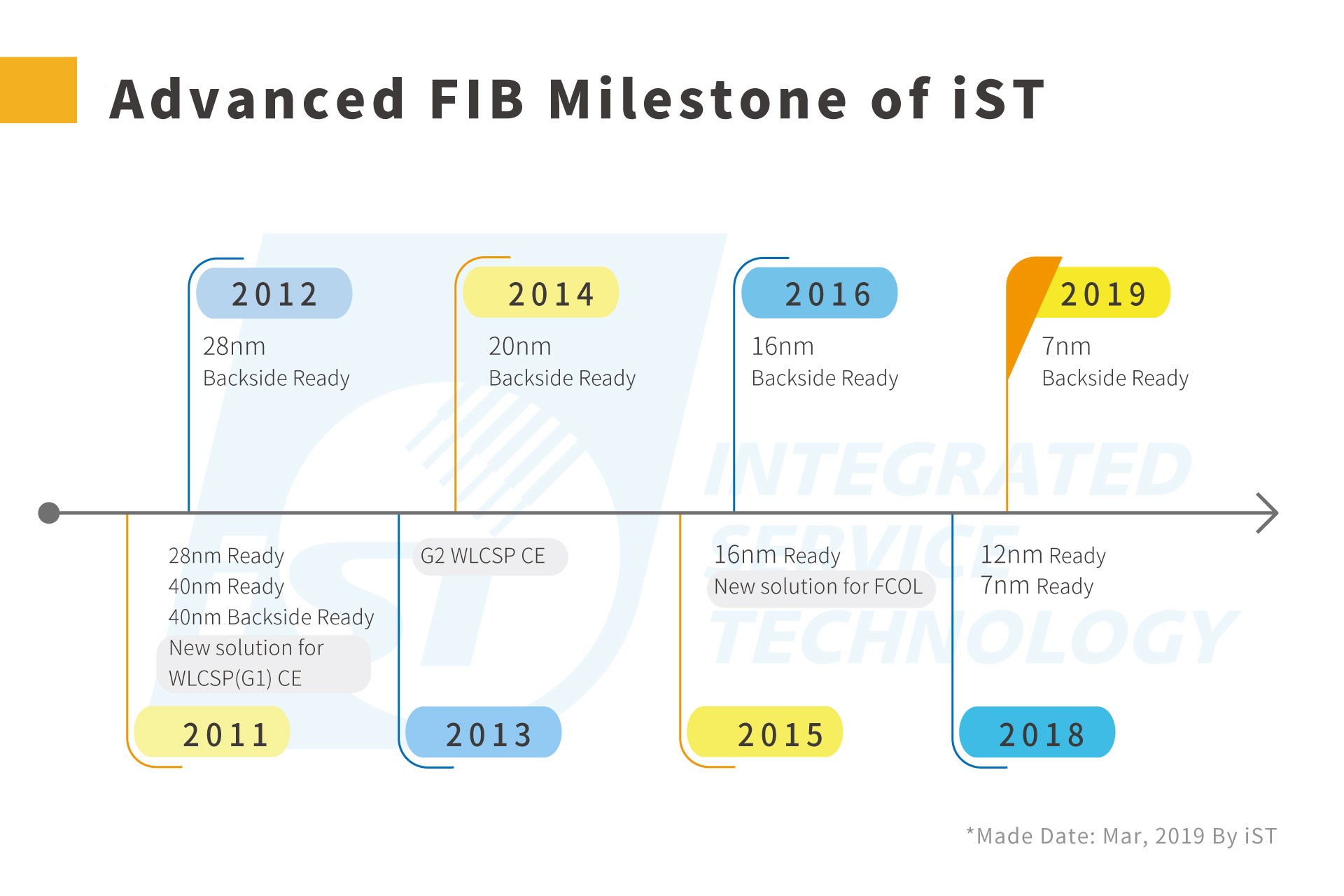

宜特表示,宜特1994年成立,從IC芯片的FIB電路修補起家,2011年即提供40/28奈米(nm)先進工藝 電路修補技術,2015年時完成20/16奈米(nm)芯片正面的電路修補技術,并于2016年挑戰完成16奈米(nm)的IC 晶背(Backside)FIB電路修補技術。2018年完成12奈米(nm)修補。

今年,宜特FIB電路修補技術再突破,成功完成7奈米(nm)工藝 的back-side電路修補,協助先進工藝芯片設計業者在電路驗證、偵錯、失效分析上更直接、靈活且快速的選擇,加速產品上市時間(Time-To-Market)。

圖說:宜特FIB電路修補技術各階段里程碑

評論