卷積編碼及Viterbi 解碼的FPGA 實現及應用

5 卷積碼譯碼--Viterbi 譯碼的FPGA 實現

Viterbi算法的基本實現方法如下:在不同時刻,按照最大似然準則將網格圖中所有的路徑進行比較,保留一條具有最大似然值的路徑(幸存路徑),同時舍棄其他路徑。每個時刻進行相同的操作,對每接收到的一段數據進行計算、比較并保存幸存路徑,最后留下的路徑就是所要求得的譯碼值。

對于卷積碼(2,1,7),其編碼的狀態數為26,所以在譯碼時,譯碼器最多需要保留26條幸存路徑,和它所對應的路徑度量值。由于是(2,1,7)編碼每個節點將引出兩條支路,但通過比較似然函數的累加值后,可以丟棄一半的路徑,使得留存下來的路徑總數保持不變。這樣在具體實現時可以開辟固定大小的存儲區,有利于硬件資源的估計。

在工程實現中采用迭代的方法,在每個時刻,對進入每個狀態的所有路徑的量度值進行比較,同時把具有最大量度值的路徑存儲下來。具體步驟如下:

(1)初始化,從時刻t = n 起,計算每個狀態的路徑和路徑度量,并存儲。

(2)在t + 1 時刻,接收新的一組數據,將當前的路徑度量與前一時刻的度量相加,求得并保存最大度量并保存幸存路徑,刪除其余路徑(3)當t L + n( L 為反饋深度)時重復步驟(2),否則結束輸出結果。

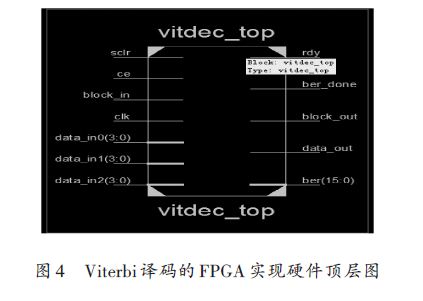

由于軟判決可以對信道噪聲進行更好的估計,因此它比硬判決有著更好的譯碼性能。因此,本文Viterbi譯碼器采用軟判決算法,同時對信號采用線性(均勻)八電平量化。其FPGA的實現圖如圖4所示。

6 系統應用

在一般的通信系統中卷積編碼和Viterbi譯碼可以是連續的,但在實際系統的應用中由于系統采用PCM分幀的模式傳送,因此卷積碼編碼和Viterbi譯碼也相應改成按幀傳送模式。由于卷積碼的編碼是數據前后相關的一種編碼模式,在按幀發送后設編碼和解碼的初始狀態均為0,如(2,1,7)編碼舉例,從編碼的原理圖2中可以清楚的看到,在相同的信道狀態和傳輸數據一定的條件下,每一幀都將影響最后6 b 數據解碼的正確性。

為此可以有兩種解決方式:

(1)為每幀數據添加固定的6 b 數據,這種做法增加了系統的數據冗余;

(2)編碼端不做任何處理,影響系統的誤碼率。

考慮到系統性能,由于系統傳輸能力還有剩余因此采用第一種處理方法。同時加入6 b 數據全部為0,這樣不僅解決了數據誤碼率的問題同時保持了解碼初始狀態的一致性,使解碼能更好的同步,有效地提高解碼的正確性。

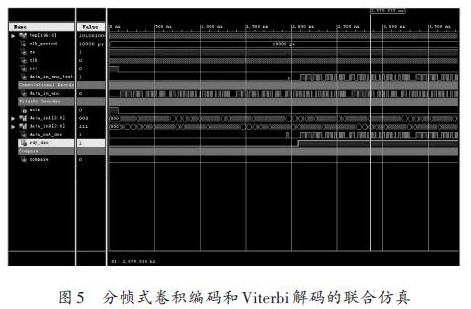

分幀式卷積編碼及Viterbi 解碼的FPGA 實現的聯合仿真如圖5所示。

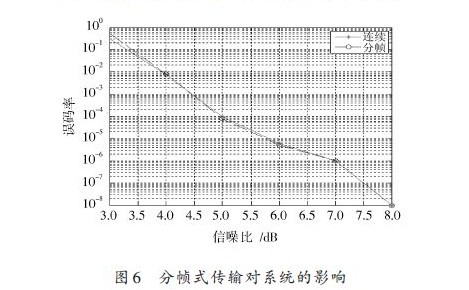

分幀式傳輸對系統的影響如圖6所示。

7 結論

在實際通信系統中,通過測量比較,分幀式編解碼和連續編解碼相比,在信道傳輸中對系統影響不大,在某些情況下分幀式編解碼甚至會優于連續編解碼。

評論