卷積編碼及Viterbi 解碼的FPGA 實(shí)現(xiàn)及應(yīng)用

0 引言

本文引用地址:http://www.104case.com/article/201809/388578.htm在現(xiàn)代通信系統(tǒng)中,信道編碼技術(shù)得到了廣泛的應(yīng)用。卷積碼結(jié)構(gòu)簡(jiǎn)單,硬件實(shí)現(xiàn)容易,同時(shí)有著較好的查錯(cuò)糾錯(cuò)能力,因此在無線通信中經(jīng)常使用,而其解碼方式常用Viterbi譯碼。

1 卷積編碼

卷積碼(Convolutional Coding)是由PgElias 于20 世紀(jì)50年代提出的一種非分組碼。它實(shí)現(xiàn)非常簡(jiǎn)單,將要發(fā)送的信息序列經(jīng)過一個(gè)特定的線性移位寄存器,即完成了編碼。

卷積編碼常用(n,k,m) 表示,一般n 和k 的值都比較小,其中m 為編碼約束長(zhǎng)度,它表示編碼時(shí)相應(yīng)的信息比特在編碼器中停留的時(shí)間。卷積編碼是一種前后相關(guān)聯(lián)的編碼過程,編碼后的碼元和當(dāng)前的k 個(gè)比特位相關(guān),同時(shí)也與前m - 1 個(gè)輸入比特相關(guān),使得相互關(guān)聯(lián)的碼元達(dá)到m × n 個(gè)。衡量卷積碼性能的兩個(gè)重要參數(shù)是碼率 (k n)和約束長(zhǎng)度。

2 卷積碼的描述方法

卷積碼的編碼描述方法有很多,工程中最常用的是寄存器網(wǎng)絡(luò)結(jié)構(gòu)法、碼多項(xiàng)式法和狀態(tài)圖形表示法。

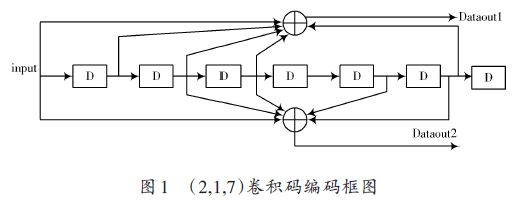

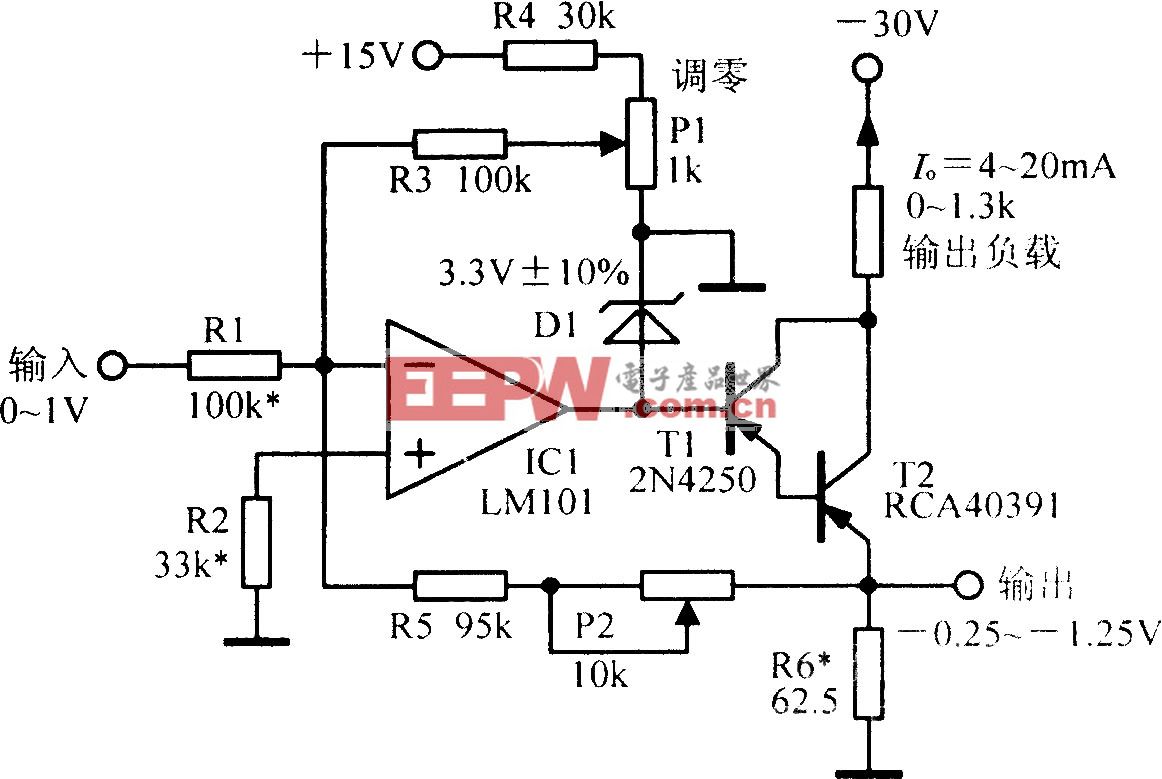

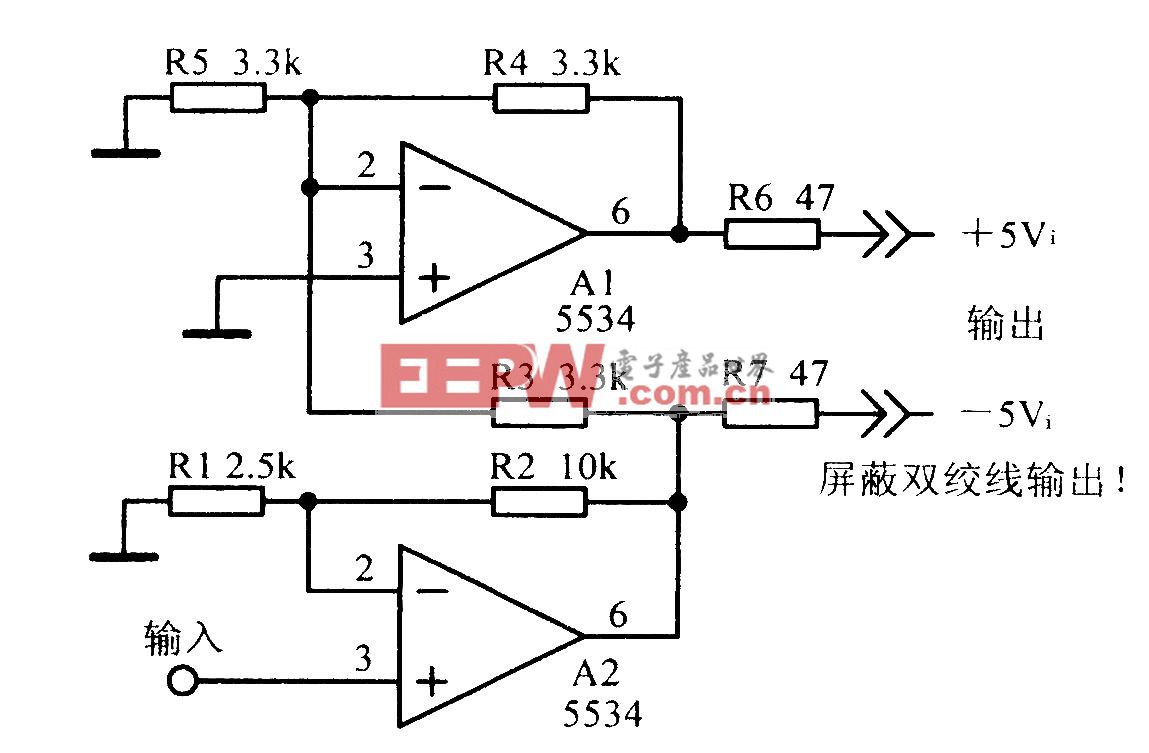

如本系統(tǒng)中使用的(2,1,7)卷積編碼,它的寄存器網(wǎng)絡(luò)結(jié)構(gòu)法表示如圖1所示。

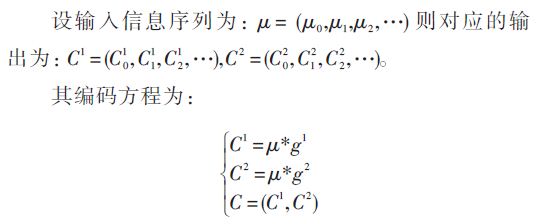

離散卷積法表示如下:

其中卷積運(yùn)算用*表示, g1,g2 為脈沖沖激響應(yīng)。則如圖1中可以表示為:

3 卷積碼的譯碼

由于卷積碼自身沒有嚴(yán)格的代數(shù)結(jié)構(gòu),其譯碼過程相對(duì)復(fù)雜。目前常用的方法有兩類:

(1)代數(shù)解碼。這種解碼方式是利用編碼本身的代數(shù)結(jié)構(gòu)進(jìn)行解碼,但不考慮信道的統(tǒng)計(jì)特性;(2)概率解碼。這一解碼方式則充分利用了信道的統(tǒng)計(jì)特性。目前常用的有Viterbi譯碼、最大后驗(yàn)概率譯碼(MAP)以及它的改進(jìn)算法Max_log_MAP等。本文采用的是Viterbi譯碼簡(jiǎn)稱(VB)。

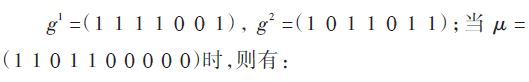

對(duì)于(n,k,m) 的二進(jìn)制卷積碼,編碼輸入的信息序列是獨(dú)立等概率的,比較各種條件下的概率,即似然函數(shù)P(R|U(m)),選擇其中概率最大的,所得就是譯碼值,它具有最小差錯(cuò)概率。其中R 是實(shí)際接收到的序列,U(m) 是可能的發(fā)送序列。當(dāng)滿足P(R|U(m′)) =max P(R|U(m)) 條件時(shí),U(m′) 就是譯碼值。

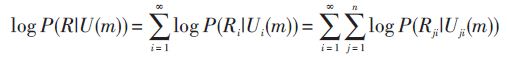

假設(shè)加性高斯白噪聲作為系統(tǒng)噪聲,同時(shí)信道是無記憶性,則卷積碼的似然函數(shù)為:

式中:Ri 是接收序列R 的第i 個(gè)分支;Ui (m) 是特定碼字U(m) 的第i 個(gè)分支;rji 是Ri 的第j 個(gè)碼元;uji (m) 是Ui (m) 的第j 個(gè)碼元,每個(gè)分支由n 個(gè)碼元組成。在工程實(shí)踐中通常用對(duì)最大似然函數(shù)取對(duì)數(shù),以加法代替乘法。對(duì)數(shù)的最大似然函數(shù)定義為:

當(dāng)log P(R|U(m)) 的值最大時(shí),譯碼成功。Viterbi譯碼利用了編碼網(wǎng)絡(luò)圖的特殊結(jié)構(gòu),降低了計(jì)算的復(fù)雜度,但它本質(zhì)上仍然是最大似然譯碼。算法實(shí)際執(zhí)行時(shí),邊接收邊比較,同時(shí)去除不可能成為最大似然選擇對(duì)象的路徑,也就是說如果兩條路徑到達(dá)同一狀態(tài),被選中的是具有最佳量度的路徑。這一路徑稱為幸存路徑,對(duì)所有狀態(tài)進(jìn)行比較、選擇,拋棄不可能的路徑,從而降低了譯碼器的復(fù)雜性。譯碼從根本上說,也就是選擇具有最小距離的碼字或最大似然量度的碼字。

4 卷積碼編碼的工程實(shí)現(xiàn)

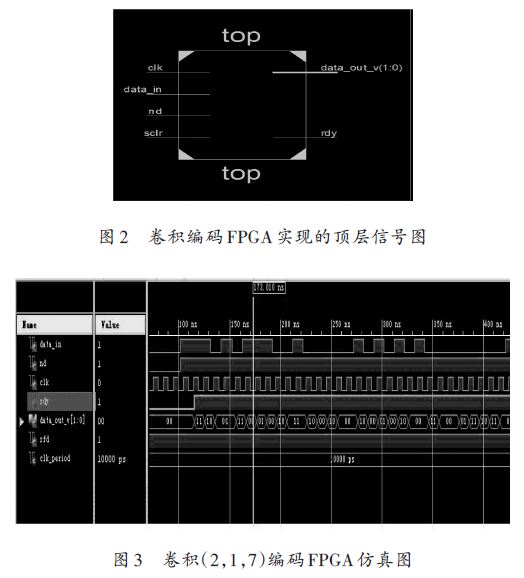

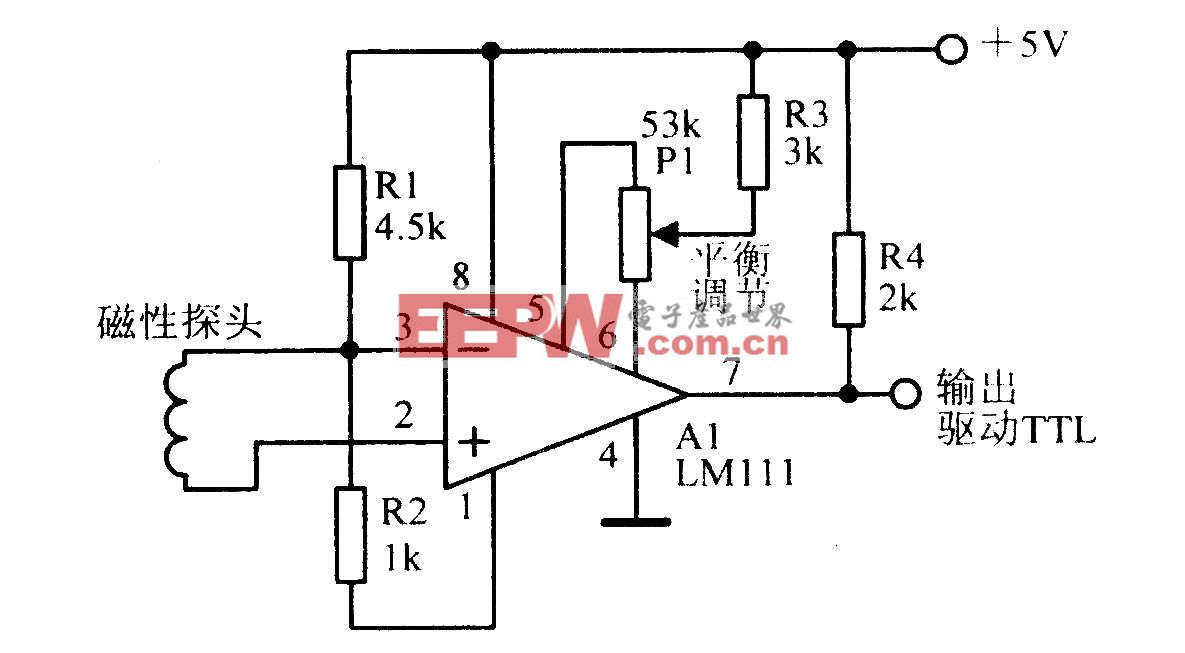

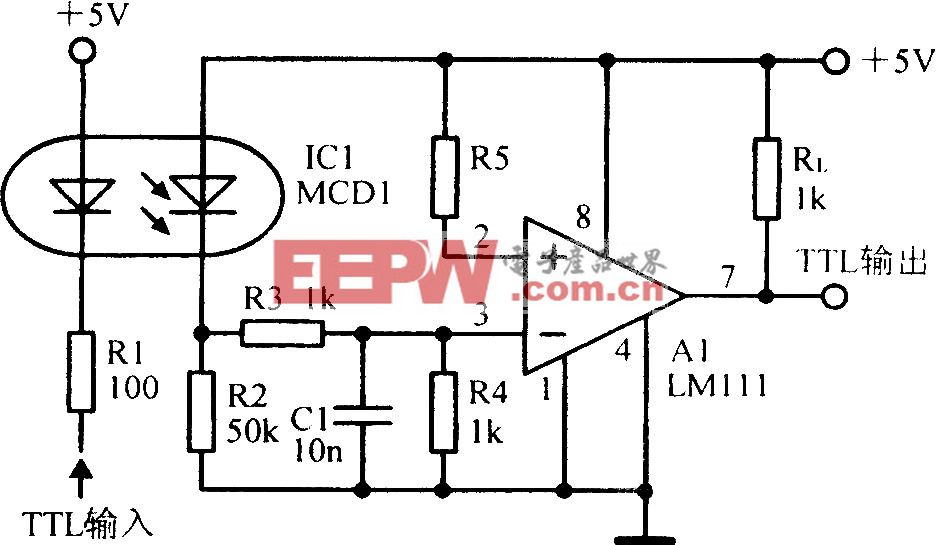

卷積碼的編碼在工程中比較簡(jiǎn)單,由移位寄存器和異或組成,系統(tǒng)中使用(2,1,7)編碼,實(shí)現(xiàn)原理如圖2所示。在FPGA中的仿真如圖3所示。

評(píng)論