FPGA電源定序電路原理分析

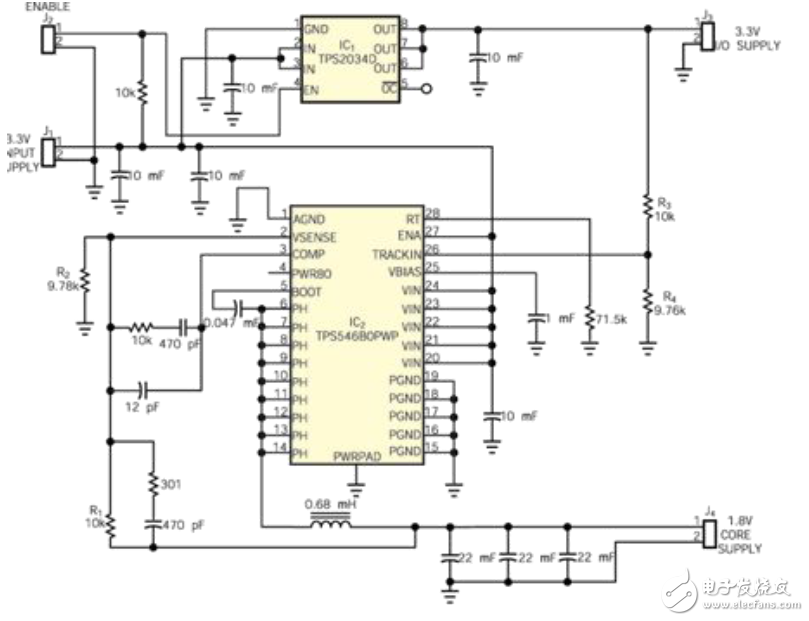

系統(tǒng)設(shè)計(jì)師必須考慮加電和斷電期間芯核電源和I/O 源之間的定時(shí)差和電壓差(換言之,就是電源定序)問(wèn)題。當(dāng)電源定序不當(dāng)時(shí),就有可能發(fā)生閉鎖失靈或電流消耗過(guò)大的現(xiàn)象。如果兩個(gè)電源加到芯核接口和I/O 接口上的電位不同時(shí),就會(huì)出現(xiàn)觸發(fā)閉鎖。定序要求不相同的FPGA 和其他元件會(huì)使電源系統(tǒng)設(shè)計(jì)更加復(fù)雜化。為了排除定序問(wèn)題,你應(yīng)當(dāng)在加電和斷電期間使芯核電源和I/O 電源之間的電壓差最小。圖1 所示的電源將3.3V 輸入電壓調(diào)節(jié)到1.8V 芯核電壓,并在加電和斷電期間跟蹤3.3V I/O 電壓,以使兩電源線(xiàn)之間的電壓差最小。

本文引用地址:http://www.104case.com/article/201710/369317.htm

圖1 這種電源定序電路可消除閉鎖問(wèn)題,并可減少FPGA 起動(dòng)瞬態(tài)電流。

電路原理:圖1 所示電源包含IC1 和IC2 兩塊IC,它們分別是TPS2034($1.0037) 電源開(kāi)關(guān)和TPS54680($3.6000)降壓型開(kāi)關(guān)穩(wěn)壓器。IC1 產(chǎn)生IC2 在起動(dòng)期間跟蹤的慢斜坡電壓。6ms 的斜坡時(shí)間可使加到電源開(kāi)關(guān)大電容和電源輸出端的涌入電流降到最小值。慢斜坡電壓能使FPGA 吸收的瞬態(tài)電流最小。電源開(kāi)關(guān)TPS2034($1.0037) 確保在IC2 具有足夠大的偏置電壓運(yùn)作并產(chǎn)生芯核電壓之前,I/O 電壓不會(huì)加到負(fù)載上。假如J1 的輸入電壓為3.3V,則J2 連接器上的電壓浮動(dòng)就會(huì)使IC1 起動(dòng)。I/O 電源電壓J3 就慢慢上升,直到達(dá)到3.3V 為止。由于I/O 電壓上升,芯核的電源電壓相應(yīng)升高,直到1.8V 為止(圖2)。TPS54680($3.6000) 的TRACKIN 引腳內(nèi)包含有一個(gè)模擬多路轉(zhuǎn)換器,以便實(shí)現(xiàn)跟蹤功能。P 在加電和斷電期間,當(dāng)TRACKIN 引腳上的電壓低于0.891V 內(nèi)部基準(zhǔn)電壓時(shí),TRACKIN 引腳上的電壓就連接到誤差放大器的非倒相節(jié)點(diǎn)。當(dāng)TRACKIN 引腳電壓低于0.891V 時(shí),該引腳就能有效地起開(kāi)關(guān)穩(wěn)壓器的基準(zhǔn)作用。連接TRACKIN 引腳的R3 和R4 電阻分壓器必須等于反饋補(bǔ)償回路中的R1 和R2 分壓器,才能在加電和斷電期間以最小的電壓差進(jìn)行跟蹤。TPS2034($1.0037) 具有37mΩ的導(dǎo)通電阻,并能提供2A 那么大的輸出電流。

評(píng)論