FPGA實戰開發技巧(8)

5.4 大規模設計帶來的綜合和布線問題

FPGA 設計的時序性能是由物理器件、用戶代碼設計以及EDA 軟件共同決定的,忽略了任何一方面的因素,都會對時序性能有很大的影響。本節主要給出大規模設計中,賽靈思物理器件和EDA 軟件的最優使用方案。

本文引用地址:http://www.104case.com/article/201710/365612.htm1)IO 約束技巧

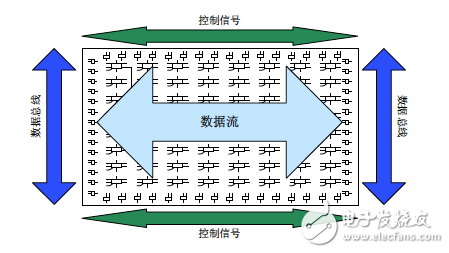

優秀設計必須要考慮IO 約束的技巧。對于賽靈思器件來講,進位鏈是垂直分布的、邏輯排列塊之間也有水平方向上三態緩沖線的直接連接、且硬核單元基本都是按列分布( 在水平方向就具備最短路徑),因此最優的方案為:將用于控制信號的I/O 置于器件的頂部或底部,且垂直布置;數據總線的I/O 置于器件的左部和右部,且水平布置,如圖5-16 所示。

圖5-16 賽靈思器件的最佳IO布局示意圖

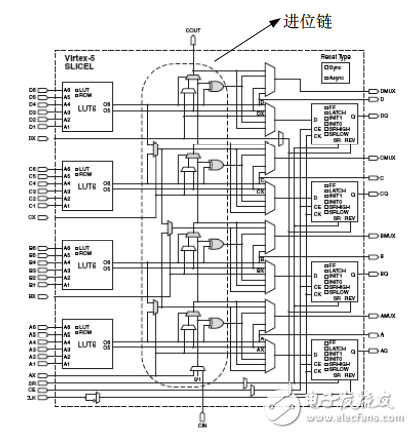

這種IO 分配方式充分利用了Xilinx FPGA 芯片架構的特點,如進位鏈排列方式以及塊RAM、硬核乘法器位置。進位鏈的結構如圖5-17 所示。能解決多位寬加法、乘法從最低位向最高位的進位延時問題;塊RAM 和硬核乘法器可節約大量的邏輯資源且保證時序,二者在FPGA 芯片中都是自上而下成條狀分布,因此數據流水平、控制流垂直可最大限度地利用芯片底層架構。當然,在實際系統設計中,可能無法完全做到上述要求,但還是應該盡可能地將高速率、多位寬的信號布置在芯片左右兩側。

圖5-17 賽靈思器件的進位鏈結構示意圖

2)ISE 的實現工具

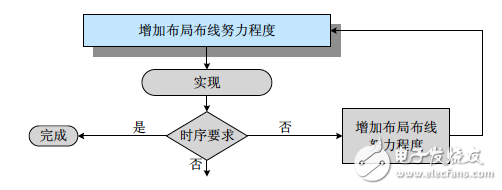

ISE 中集成的實現工具具備不同的努力程度(Effort Level),當然使用最高級別的,可以提高時序性能,而不必采取其它措施( 如施加更高級的時序約束,使用高級工具或者更改代碼等),但需要花費很長的計算時間。為此,賽靈思推薦的最佳流程如圖5-18 所示。

圖5-18 賽靈思實現工具的最佳使用策略

在第一遍實現時,使用全局時序約束和缺省的實現參數選項,如果不能滿足時序要求,則可嘗試以下方法:

(1) 嘗試修改代碼,如使用合適的代碼風格,增加流水線等;

(2) 修改綜合參數選項,如OpTImizaTIon Effort,Use Synthesis Constraints File,Keep Hierarchy,Register

DuplicaTIon,Register Balancing 等;

(3) 增加實現工具的努力程度;

(4) 在綜合和實現時采用指定路徑時序約束的方法。

實現工具分為映射(MAP) 和布局布線(PAR) 兩部分,和PAR 一樣,也可使用Map-TIming 參數選項針對關鍵路徑進行約束。如:參數“Timing-Driven Packing and Placement”給關鍵路徑以優先時序約束的權利;用戶約束通過翻譯(Translate) 過程從User Constraints File (UCF ) 中傳遞到設計中。

評論