使用QDR-IV設計高性能網絡系統之二

在本系列第一部分,我們探討了兩種類型的QDR-IV存儲器、時鐘、讀/寫操作和分組操作。在第二部分,我們將探討總線轉換、總線翻轉、地址奇偶校驗等重要的總線問題。

總線轉換的注意事項

總線轉換時間非常重要,其決定了讀和寫指令間是否需要額外的間隔來避免在同一個I/O 端口上發生總線沖突。

想象下QDR-IV HP SRAM 中端口A 先后收到寫指令和讀指令。從CK 信號的上升沿(與初始化寫指令周期相對應)算起,在整整三個時鐘周期后向DQA 引腳提供寫數據。讀數據則將在下一個周期發送,因為 DQ從CK 信號的上升沿(與初始化讀指令的周期相應)算起五個時鐘周期后才能獲得數據。此外,為符合總線轉換時間和傳輸時延(從ASIC/FPGA 到QDR IV 存儲器),還有兩個額外周期。因此,啟動寫指令后,可以立即啟動讀指令。

在其他情況下,如果先啟動讀指令后啟動寫指令,那么發送讀指令經過三個時鐘周期后,才能發送寫指令。這是因為,從在時鐘信號CK 的上升沿上對讀指令進行采樣算起,經過五個周期后可獲得DQA 引腳上的讀數據,并且從在時鐘信號CK 的上 升沿上對寫指令進行采樣算起,在整三個時鐘周期內向DQA 引腳提供寫數據。否則,將會發生總線沖突。因此,發送寫指令后的最小時鐘周期應該為RL – WL + 1(RL:讀時延;WL:寫時延;這兩個時延的單位為時鐘周期數)。另外一個時鐘周期用于正確捕獲數據并補償總線轉換時延(通常為一個時鐘周期)。

如果傳輸時延大于總線轉換時延,那么‘讀到寫’指令間的間隔為:

“讀到寫”指令間的時間周期 = 讀時延 – 寫時延 + 1 + 傳輸時延

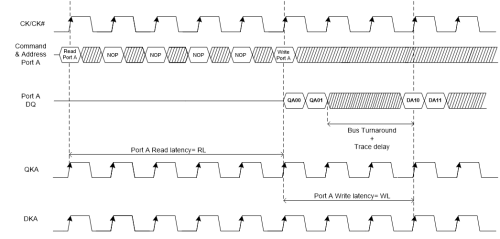

請參考圖7。發送讀指令經過四個時鐘周期后,將發送端口A 的寫指令。這樣是為了避免因讀/寫時延、總線轉換時間和傳輸時延間的差別而導致的總線沖突。

圖7. QDR-IV HP SRAM時序分析圖

總線翻轉

QDR-IV 器件支持總線翻轉以降低切換噪聲和I/O功耗。在存儲事務處理中,存儲器控制器和QDR-IV都可以選擇應用總線翻轉。

由于QDR-IV 器件的POD 信令模式為I/O 信號提供了到VDDQ 的高壓終端選項,所以信號轉為高電平邏輯狀態不會耗電。因此,總線翻轉對于POD I/O 信號是一個很重要的性能。QDR-IV 會保證翻轉地址和數據總線的數據完整性。

使用芯片配置寄存器來啟用或禁用地址和數據總線翻轉功能。

地址總線翻轉

AINV 是雙倍數據速率信號,每次將地址發送給存儲器器件時都會更新該信號。AINV 引腳指示是否對地址總線(An –A0)和AP 進行了翻轉。AINV 是高電平有效信號。當AINV = 1 時,將翻轉地址總線;當AINV = 0 時,不翻轉地址總線。AINV 引腳的功能由存儲器控制器控制。

地址總線和地址奇偶位都被視為地址組(AG)。

表5顯示的是AG 定義以及x18 和x36 QDR-IV 選項的AINV 設置條件。

表5. 地址總線翻轉條件

x18 | x36 | ||

地址群 | AG[22:0] = A[21:0],AP | AG[21:0] = A[20:0],AP | |

翻轉邏輯 |

| 如果AG[21:0]中邏輯“0”的數量≥11,將AINV置為1,這時會對AG[21:0]進行翻轉 | |

如果AG[22:0]中邏輯“0”的數量12,將AINV置為0,這時不會翻轉AG[22:0] | 如果AG[21:0]中邏輯“0”的數量11,將AINV 置為0,這時不會翻轉AG[21:0] |

x36器件示例

不進行地址總線翻轉:

假設要訪問的地址分別為22’h 000199和22’h 3FFCFF。17個地址引腳需要在第一個和第二個地址的邏輯狀態間進行切換,如下表所示(紅色單元格顯示)。這樣會增大地址引腳上的切換噪聲、I/O電流以及串擾。

表6. 地址總線序列(未進行總線翻轉)

AG[21:0] | 22位(二進制) | |||||||||||||||||||||

第一個地址組- 22h 000199 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 |

第2個地址組 - 22h 3FFCFF | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

進行地址總線翻轉:

根據表5顯示,第一個地址組(22h 000199)滿足翻轉邏輯條件。因此,存儲器控制器發送第一個地址組前,它會將地址組從22’h 000199翻轉為22’h 3FFE66,并將AINV引腳置為1。由于不需要翻轉第二個地址組,所以存儲器控制器可以將其直接發送,并將AINV設置為0。

下表顯示的是地址總線翻轉的結果。在這種情況下,只有5個地址引腳需要切換邏輯(紅色單元格顯示)。切換位的總數降低為5,所以降低了由于同時切換輸出(SSO)而引起的噪聲、I/O電流以及串擾。

表7. 地址總線序列(進行總線翻轉)

AG[21:0] | 22位(二進制) | AINV | |||||||||||||||||||||

第一個地址組 - 22h 3FFE66(翻轉后) | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 1 |

第二個地址組 - 22h 3FFCFF(保持不變) | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

數據總線翻轉

數據總線翻轉在數據線路中也類似,但翻轉位由存儲器控制器在存儲器寫操作期間生成,并且翻轉位由QDR-IV存儲器中的翻轉邏輯在存儲器讀操作期間生成。

DINVA和DINVB引腳指示了是否翻轉相應的DQA和DQB引腳。DINVA和DINVB均為高電平有效信號。當DINV = 1時,將翻轉數據總線;當DINV = 0時,不翻轉數據總線。

DINVA[1]和DINVA[0]相互獨立并控制與其相應的DQA組。DINVA[0]控制DQA[17:0](對于x36的配置)或DQA[8:0](對于x18的配置)。DINVA[1]控制DQA[35:18](對于x36的配置)或DQA[17:9](對于x18的配置)。同樣,DINVB[0]控制x36配置中的DQB[17:0]或x18配置中的DQB[8:0]。DINVB[1]控制x36配置中的DQB[35:18]或x18配置中的DQA[17:9]。

表8顯示的是DINV位說明以及x18和x36 QDR-IV選項的DINVA設置條件。

表8. 數據總線翻轉條件

x18 | x36 | |

DINV位 | DINVB[1]控制DQB[17:9], DINVB[0]控制DQB[8:0] | DINVA[1]控制DQA[35:18], DINVA[0]控制DQA[17:0] DINVB[1]控制DQB[35:18], DINVB[0]控制DQB[17:0] |

翻轉邏輯 | 如果DQA[8:0]中的邏輯“0”數量 ≥ 5,將DINVA[0]設置為1,這時會對DQA[8:0]進行翻轉 | 如果DQA[17:0]中的邏輯“0”數量 ≥ 10,將DINVA[0]設置為1,這時會對DQA[17:0]進行翻轉 |

如果DQA[8:0]中的邏輯“0”數量 5,那么不對DQA[8:0]進行翻轉并將DINVA[0]設置為0 | 如果DQA[17:0]中的邏輯“0”數量 10,那么不對DQA[17:0]進行翻轉,并將DINVA[0]設置為0 |

注意:可以對DINVA[1]、DINVB[0]以及DINVB[1]使用相同的翻轉邏輯,以便控制相應的DQ組。

x18器件的示例

不進行數據總線翻轉:

假設需要分別發送DQA[8:0]上的9’h 007和9’h 1F3。6個數據引腳需要在第一個和第二個DQA[8:0]位的邏輯狀態之間進行切換,如下表所示(紅色單元格顯示)。這樣會增大數據引腳上的切換噪聲、I/O電流以及串擾。

表9. 數據總線序列(不進行總線翻轉)

DQA[8:0] | 9位(二進制) | ||||||||

第一個DQA[8:0] - 9h 007 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 |

第二個DQA[8:0] - 9h 1F3 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 |

進行數據總線翻轉:

根據表8,第一個DQA[8:0]滿足翻轉邏輯條件。因此,存儲器控制器發送第一個DQA[8:0]前,它會將引腳地址從9’h 007翻轉為9’h 1F8,并將DINVA[0]引腳設置為1。由于第二個DQA[8:0]不需要翻轉,所以存儲器控制器可以直接發送它,并將DINVA[0]設置為0。

表10顯示的是數據總線翻轉的結果。在這種情況下,只有3個數據引腳需要切換邏輯(紅色單元格顯示)。切換位的總數降低為3,所以降低了SSO的噪聲、I/O電流以及串擾。

表10. 數據總線序列(進行總線翻轉)

DQA[8:0] | 9位(二進制) | DINVA[0] | ||||||||

第一DQA[8:0] - 9h 1F8(翻轉后) | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 |

第二個DQA[8:0] - 9h 1F3(保持不變) | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 0 |

QDR-IV只有一條地址總線,但其以雙倍數據速率和高頻率運行。因此,地址奇偶校驗輸入(AP)和地址奇偶校驗錯誤標志輸出(PE#)引腳提供了片上地址奇偶校驗功能,以便能夠確保地址總線完整性。地址奇偶校驗功能是可選的;可以使用配置寄存器來啟用或禁用它。

通過該AP引腳可以在各地址引腳(An到A0)上進行偶校驗。設置AP值,使AP和An-A0中邏輯“1”的總數為偶數。

對于數據總線寬度為x18的器件,設置AP值,使A[21:0]和AP中邏輯“1”的總數為偶數。

對于數據總線寬度為x36的器件,設置AP值,使A[20:0]和AP中邏輯“1”的總數為偶數。

器件的示例

以數據總線寬度為x36的器件的21’h1E0000和21’h1F0000地址為示例。表11顯示的是如何為每個地址設置AP值。

表11. 地址奇偶功能

| AP | A[20:0]和AP中邏輯“1”的 總數 | |||||||||||||||||||||||

21h1E0000 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 4 | 因為在A[20:0]中邏輯“1”的總數為偶數(4) | |

21h1F0000 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 6 |

| |

當發生奇偶錯誤時,在配置寄存器4、5、6和7中(請查看相關數據手冊,了解有關配置寄存器的更多信息)記錄第一個錯誤的完整地址以及端口A/B錯誤位和地址翻轉位。端口A/B錯誤位表示發生地址奇偶錯誤的端口:0表示端口A,1表示端口B。持續鎖存該信息,直到向配置寄存器3中的地址奇偶錯誤清除位寫入1來清除該信息為止。

通過兩個計數器,可以表示是否發生了多個地址奇偶錯誤。端口A錯誤計數是端口A地址上奇偶錯誤數量的運行計數器。同樣,端口B錯誤計數是端口b地址上奇偶錯誤數量的運行計數器。每個計數器獨立計數到最大值(3),然后將停止計數。這些計數器均是自由運行的;對配置寄存器3的地址奇偶錯誤清除位寫入1,可將其復位。

檢測到地址奇偶錯誤后,寫操作就會被忽略,以防止損壞存儲器。但是,如果輸入地址錯誤,仍會繼續執行讀操作,但存儲器會發送出假數據。

PE#為低電平有效信號,表示地址奇偶錯誤。檢測到地址奇偶錯誤后,PE#信號在8個周期(QDR-IV XP SRAM)或5個周期(QDR-IV HP SRAM)內被設置為0。它將保持置位狀態,直到通過配置寄存器清除了錯誤為止。處理完地址翻轉便表示完成了地址奇偶檢查。

PE#轉為低電平后,會停止存儲器操作,并使用配置寄存器將PE#復位為高電平。此外,由于發生AP錯誤的寫操作也被阻止,所以需要向存儲器重新編寫數據。

在本系列第三部分,我們將探討校正問題,其中包括矯正訓練、控制/地址校正和讀寫校正,以及糾錯碼(ECC)和QDR-IV存儲器控制器的設計建議。

評論