基于FPGA的PWM計數(shù)器改進(jìn)設(shè)計

簡單改變FPGA計數(shù)器規(guī)格使作為DAC功能PWM計數(shù)器的紋波降低。

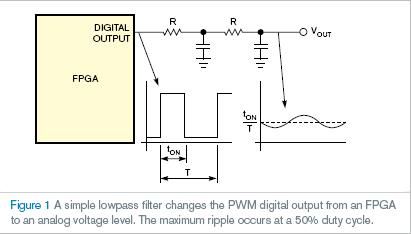

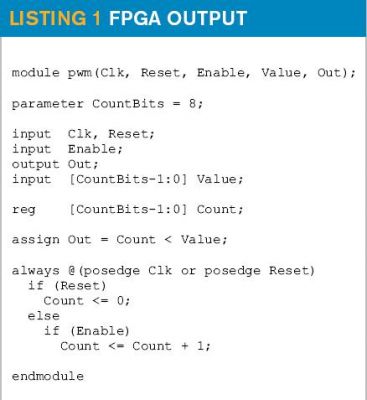

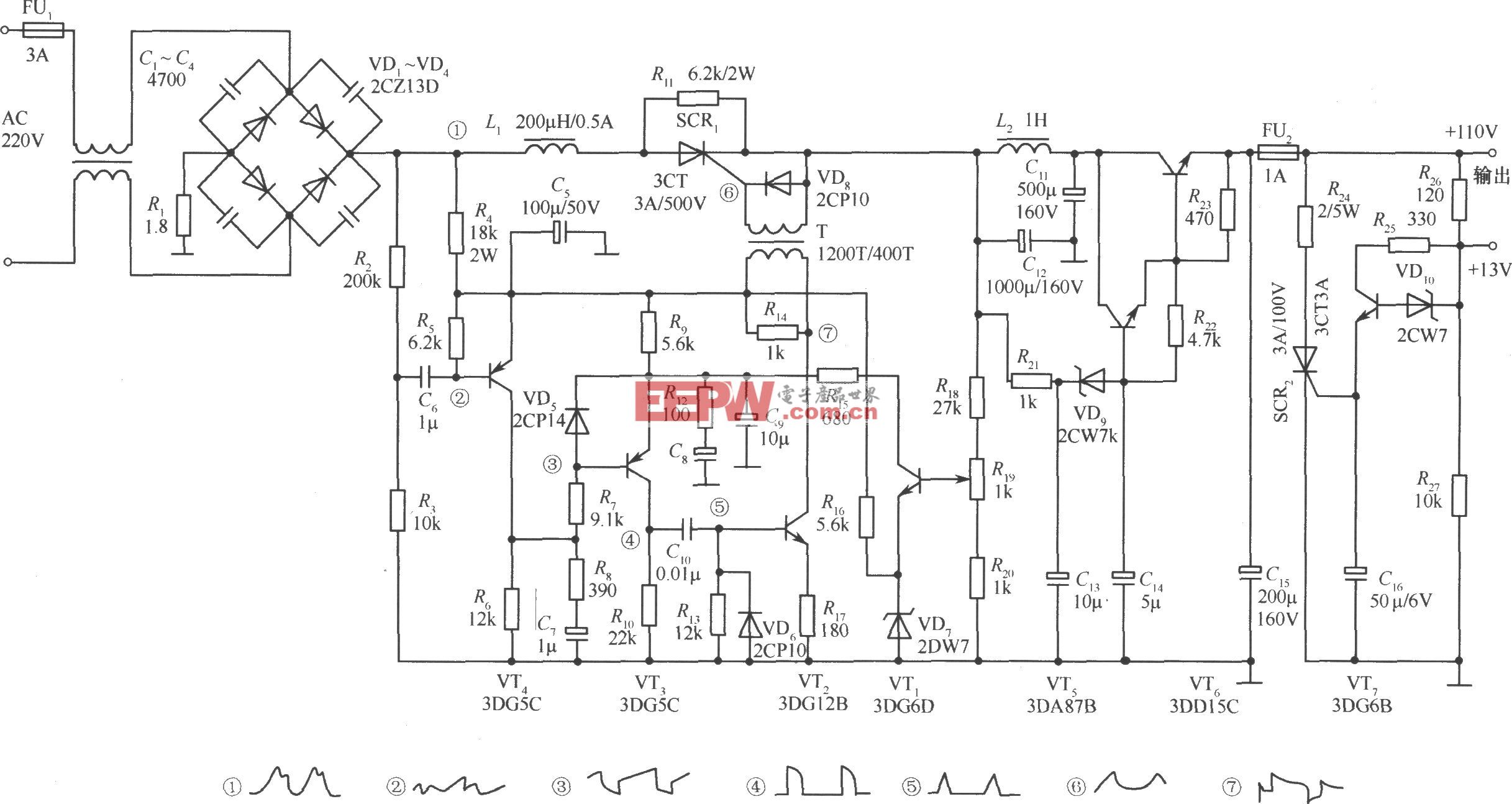

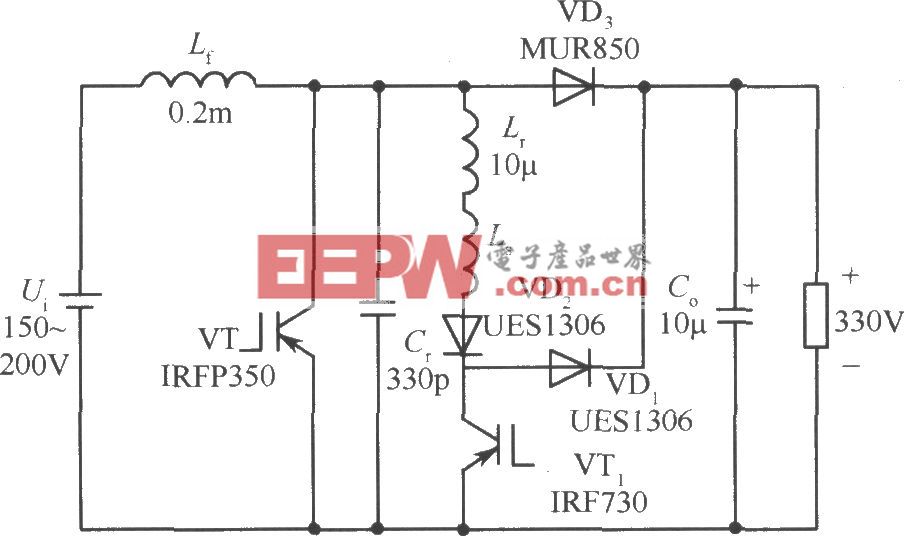

本文引用地址:http://www.104case.com/article/201706/349045.htm 當(dāng)需要一些模擬輸出和系統(tǒng)中有FPGA時,很可能選擇使用如圖1的PWM模塊和簡單低通濾波器。FPGA的輸出是固定頻率、計數(shù)器和數(shù)字比較器使占空比可變的典型波形(表1)。

假設(shè)高信號使能,計數(shù)器每個時鐘周期進(jìn)行計數(shù),PWM輸出的頻率為時鐘頻率的2次冪分頻。通過連接前置比例器,使用使能來降低輸出頻率。由于輸出頻率固定,濾波器容易計算。已知占空比50%時,出現(xiàn)最壞的紋波。最大紋波和上升時間的限制結(jié)合決定濾波器類型和RC(電阻/電容)值。

對表1中編碼進(jìn)行非小改動,能夠改進(jìn)PWM電路的性能。但在原先系統(tǒng)中,最大紋波電流發(fā)生在50%占空比時,最小紋波電流發(fā)生在最小占空比時,改進(jìn)的版本顯示最大紋波等于標(biāo)準(zhǔn)版的最小值。關(guān)鍵是產(chǎn)生最高頻率的可能性,還能保持平均的占空比常數(shù)。輸出脈沖頻率越高,濾波器性能越好。

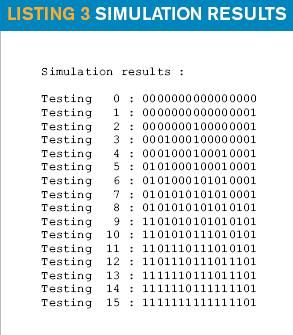

從左到右交換所有位來修改由重編二進(jìn)制比較器組成表1。MSB(最高有效位)變成LSB(最低有效位),LSB變成MSB,等等(表2)。只需重編位,而不需額外寄存器或邏輯單元。

表3顯示了4位PWM發(fā)出的脈沖序列。表3中,可以看到50%占空比時(第二列,值為8),頻率最大,為時鐘頻率的2分頻。在第一個紋波出現(xiàn)點(第二列,值為1),傳統(tǒng)PWM系統(tǒng)中有同樣的紋波,也就是說,脈沖序列是相同的。

評論