上傳原理圖和PCB圖,請教為什么DC-DC電源紋波大?

網友eefishing問題:

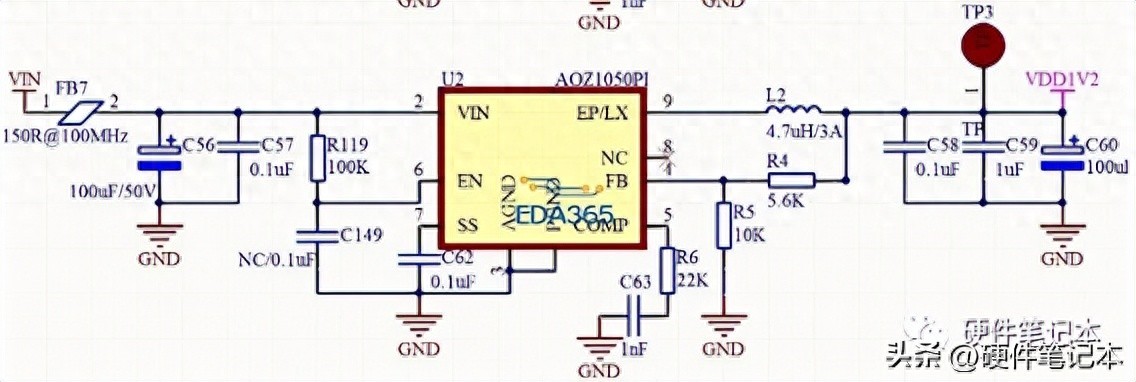

本文引用地址:http://www.104case.com/article/202412/465356.htm用AOZ1050PI設計的一款DC-DC電源轉換,輸入9~18V,輸出1.2V,AOZ1050開關頻率500KHz,現在用示波器測得輸出大概有100mV,Vp-p在485KHz左右的紋波。

請問各位專家:

1 這個指標的紋波是否在設計許可的范圍之內?在一般情況下,DC-DC電源轉換的紋波在一個什么范圍內可以認為是正常的?

2 從原理圖和PCB圖上,這個設計是否還能夠進一步優化降低紋波?還請指出。

敬請各位斧正。

網友mituone的回復:

100mV 的紋波(Ripple)對數字線路應該沒什么問題,對模擬線路就看情況了,有的線路很敏感需要更低。但芯片資料展示在滿載(Full Load)狀況下,紋波(Ripple)可以壓到 20mV 左右。

布線建議︰

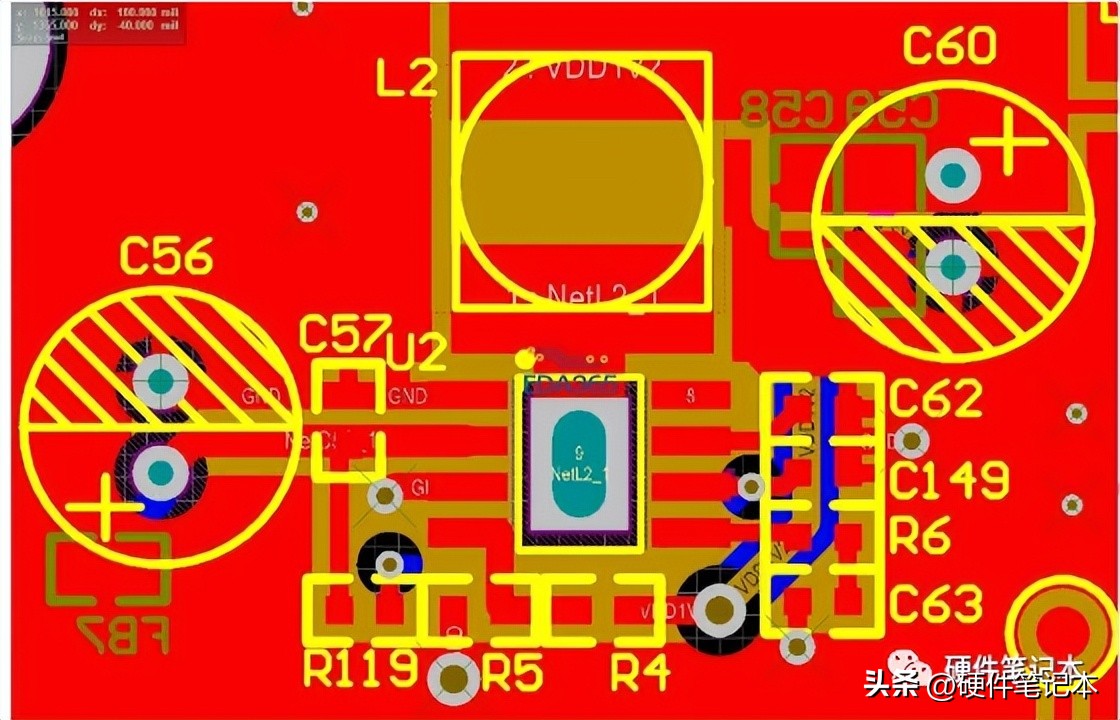

L2 在上方,但 FB 在 AOZ1050 Pin 4,造成反饋路徑繞了一大圈才回到芯片。將 L2 移到下方,可以縮短反饋路徑。

AOZ1050 Pin 3 Power Return Ground 只有單點落地顯得太單薄,要注意一盎司(oz)銅厚下,10 mil 的落孔只有 0.8A 的承受力,如果是使用十字線接地,就 4 條十字線加起來可承受的電流。宜將地鋪大,并多打導通孔與背面的地連通。

注意芯片資料上的 AOZ1050 Pin 4 PGND 與 R5 落地的畫法,它們是用不同的地符號。意思是說他們建議你用隔離的地(Isolation Ground),做法上就是 R5 和 Pin 4 拉在一起,然后單點落地。

輸出應該先過濾波電容 C58、C59 和 C60,再給其它線路,注意到你的輸入電容 C56 和 C57 就做得不錯,可以參考它的做法。

注意線寬與承載電流的關系,輸入與輸出線寬需要計算。不曉得 C60 "+" 號旁邊那條細線是做什麼用的?看起來很細。

布線大原則︰

讓輸入或輸出濾波電容和地造成的回路越短越好。

仍需檢視的部份︰

L2 電感宜選用有屏蔽(Shielding)的封裝,避免漏磁(Magnetic Leakage)干擾。

L2 電感的額定電流(IDC1 和 IDC2)宜被檢視,避免峰值電流(Peak Current)超過或溫度升高,造成電感量不足產生紋波和噪聲。

L2 直流電阻(DCR)宜被檢視,太高效率不好、容易發熱。

AOZ1050 Pin 5 COMP 上的補償電路,芯片資料上有計算公式,宜試算一下是否搭配得宜。

電解電容 C56 和 C60 的 ESR 越小越好,如果您真的很在意紋波及噪聲的大小,電解電容盡量選用可靠一點的廠牌。

評論