Verilog HDL基礎(chǔ)之:實(shí)例4 PS/2接口控制

實(shí)例的內(nèi)容及目標(biāo)

1.實(shí)例的主要內(nèi)容

本實(shí)例通過Verilog編程實(shí)現(xiàn)在紅色颶風(fēng)II代Xilinx開發(fā)板上面實(shí)現(xiàn)對鍵盤、LCD、RS-232等接口或者器件進(jìn)行控制,將有鍵盤輸入的數(shù)據(jù)在LCD上面顯示出來,或者通過RS-232在PC機(jī)上的超級終端上顯示出來。

本文引用地址:http://www.104case.com/article/201706/348842.htm2.實(shí)例目標(biāo)

通過本實(shí)例,讀者應(yīng)達(dá)到下面的目標(biāo)。

- 了解PS/2接口協(xié)議。

- 掌握鍵盤的工作原理。

- 編寫Verilog程序?qū)崿F(xiàn)通過開發(fā)板上PS/2接口讀取鍵盤的輸入信息。

原理簡介

PS/2鍵盤履行一種雙向同步串行協(xié)議。換句話說每次數(shù)據(jù)線上發(fā)送一位數(shù)據(jù),并且每在時鐘線上發(fā)一個脈沖就被讀入,鍵盤可以發(fā)送數(shù)據(jù)到主機(jī),而主機(jī)也可以發(fā)送數(shù)據(jù)到設(shè)備。但主機(jī)總是在總線上有優(yōu)先權(quán),它可以在任何時候抑制來自于鍵盤的通信,只要把時鐘拉低即可。

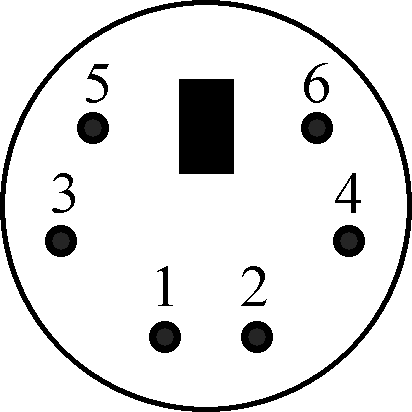

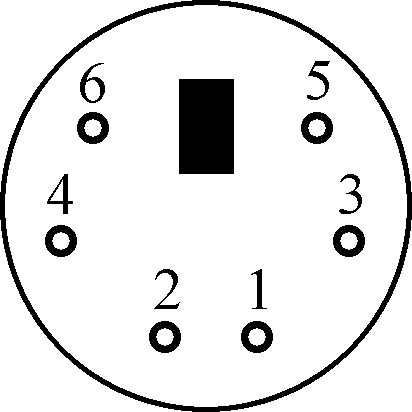

本實(shí)例要編寫一個能實(shí)現(xiàn)PS/2端口功能的Verilog程序。首先我們要了解PS/2端口的結(jié)構(gòu)與管腳功能定義,如表1所示。

表1 PS/2端口結(jié)構(gòu)及管腳定義

端 口 結(jié) 構(gòu) | 管 腳 定 義 | ||

|

| 1 | 數(shù)據(jù) |

2 | 未實(shí)現(xiàn),保留 | ||

3 | 電源地 | ||

4 | 電源,+5V | ||

5 | 時鐘 | ||

插頭 | 插座 | 6 | 未實(shí)現(xiàn),保留 |

可以看到,PS/2里面只有一個數(shù)據(jù)口,若要分辨很多按鍵就需要一個高效率的分辨方法。鍵盤的處理器花費(fèi)很多的時間來掃描或監(jiān)視按鍵矩陣。如果它發(fā)現(xiàn)有鍵被按下,釋放或按住鍵盤,將發(fā)送掃描碼的信息包到計算機(jī)。

掃描碼有兩種不同的類型:“通碼”和“斷碼”。當(dāng)一個鍵被按下或按住就發(fā)送“通碼”,當(dāng)一個鍵被釋放就發(fā)送“斷碼”。每個按鍵被分配了惟一的“通碼”和“斷碼”。這樣,主機(jī)通過查找惟一的掃描碼就可以測定是哪個按鍵。

每個鍵一整套的通斷碼組成了掃描碼集,圖1中包含了鍵盤上面大部分按鍵的掃描碼。

當(dāng)按鍵被釋放以后,鍵盤回在掃描碼前面加上一個“F0”作為按鍵松開信號。同時有的按鍵是Extended(擴(kuò)展)鍵,此時要在它們的掃描碼前面加上一個“E0”作為開頭,這種按鍵松開以后將在掃描碼前面附加上“E0F0”。

下面我們來了解信號是如何從鍵盤輸入通過PS/2端口的數(shù)據(jù)線輸入的。首先鍵盤要檢測數(shù)據(jù)線和時鐘線是否都為高,只有它們都處在高的狀態(tài)才可以寫數(shù)據(jù)。從鍵盤發(fā)送到主機(jī)的數(shù)據(jù)在時鐘信號的下降沿(當(dāng)時鐘從高變到低)的時候被讀取。

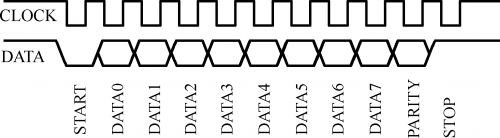

鍵盤主要使用一種每幀包含11位的串行協(xié)議:第一位是起始位,始終為“0”;接下來是8位數(shù)據(jù)位,排列順序是由低到高;再后面是奇偶校驗位;最后是結(jié)束位,始終為“1”。如圖2所示為該協(xié)議的時序圖。

圖1 鍵盤掃描碼

圖2 鍵盤串行協(xié)議

實(shí)例詳解

此處僅給出主要的操作流程。

(1)啟動ISE軟件。

(2)創(chuàng)建新工程。

(3)編寫鍵盤串行協(xié)議。

按照圖2的時序編寫相應(yīng)的Verilog代碼,具體源代碼參見實(shí)例代碼。

(4)添加設(shè)計輸入。

將編寫好的接口協(xié)議加載至工程中,完成接口控制與系統(tǒng)的對接。

(5)設(shè)置器件及管腳約束。

按照開發(fā)板的說明進(jìn)行相關(guān)的設(shè)置。

(6)下載驗證。

下載程序后,將鍵盤接至開發(fā)板上,通過開發(fā)板的LCD可以看到鍵盤輸入的字符。

評論