利用FPGA實現外設通信接口之: 利用FPGA實現常用顯示接口(Display Interface)

10.4利用FPGA實現常用顯示接口(DisplayInterface)

10.4.1七段數碼顯示接口的設計與實現

七段數碼管因為價格低廉,使用簡單,經常被用來實現一些簡單的狀態顯示功能。七段數碼管的標準外觀圖如圖10.16所示。右下角的圓點用Dp來表示,用來實現小數點的顯示。

七段數碼管經常用來顯示十進制或十六進制的數,所以在數據顯示之前,首先要進行二進制到十進制或者十六進制的轉換。將它們轉換成十進制的或是十六進制的數。

七段數碼管分為共陰和共陽兩種類型。比如,紅色颶風開發板使用的是共陰類型的數碼管,信號是高電平有效。十六進制數據在顯示的時候對應的各段輸出對應關系如表10.2所示。

表10.2 十六進制數據與輸出的映射關系

數據 | a | b | c | d | e | f | g | Dp |

0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 |

1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 |

2 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 0 |

3 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 |

4 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 |

5 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 |

6 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 0 |

7 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 |

8 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

9 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 0 |

A | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 0 |

B | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 |

C | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 0 |

D | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 |

E | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 |

F | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 |

紅色颶風開發板上采用的是4位并聯的數碼管。4個數碼管共用8條數據線,控制線是獨立的。如果4個數碼管要顯示不同的數值,比如顯示1234,那么就需要采用一種控制策略。最常用的方法就是動態掃描顯示。

動態掃描顯示利用了時分的原理和人的視覺暫留效應。例如,一個4位動態掃描數碼顯示器的顯示周期可劃分為4個階段。

階段1→階段2→階段3→階段4

每個周期只選通一位數據。在周期1顯示第一個數碼,周期2顯示第二個數碼。在掃描4個階段后,又重新按順序循環。如果掃描的速度足夠快,從視覺上看就好像4個數碼管同時顯示不同的內容。

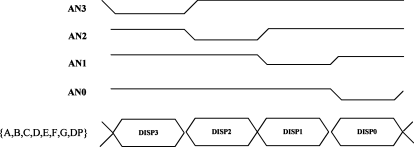

4位掃描數碼管共有4組BCD碼(4位)輸入線,8根8段譯碼輸出線和4根位選通線。掃描工作中,先從4組BCD數據中選出一組,通過BCD/7段譯碼器譯碼后輸出。與此同時,3/8譯碼器產生位選通信號,則在此瞬間,數碼管應該為要顯示的數值。然后再選出下一組數據譯碼后輸出,位選通信號則相應下移一位,將下一數碼管選通輸出,如圖10.17所示。

圖10.17動態掃描原理示意圖

10.4.2字符型LCD顯示接口的設計與實現

液晶屏(LCD)通常分為點陣型和字符型兩種。字符型的液晶屏相對于數碼管來說,可以顯示更多的內容和字符,人機界面更為友好,而且操作簡單,因此得到了廣泛的應用。不同廠家的字符型LCD雖然型號不同,但是操作方法基本是一致的。

字符型LCD一般會根據顯示字符的數量來確定型號,如1602表示這個液晶可以顯示2行字符,每行為16個。紅色颶風開發板上采用的字符型LCD的型號就是1602。下面就以1602為例來介紹字符型LCD顯示接口的設計方法。

1602型液晶模塊采用14針標準接口,各個管腳的定義如表10.3所示。

表10.3 1602型液晶模塊的管腳配置表

管腳 | 符號 | 說明 |

1 | VSS | 器件地 |

2 | VDD | +5V電源 |

3 | V0 | 對比度調整端,接正電源時對比度最弱,接地電源時對比度最高,對比度過高時會產生“鬼影”,使用時可以通過一個10kW的電位器調整對比度 |

4 | RS | 寄存器選擇,高電平時選擇數據寄存器,低電平時選擇指令寄存器 |

5 | RW | 讀寫信號線,高電平時進行讀操作,低電平時進行寫操作。當RS和RW共同為低電平時可以寫入指令或者顯示地址,當RS為低電平、RW為高電平時可以讀忙信號,當RS為高電平、RW為低電平時可以寫入數據 |

6 | E | 使能端,當E端由高電平跳變成低電平時,液晶模塊執行命令 |

7~14 | D0~D7 | 8位雙向數據線 |

1602液晶模塊內部的字符發生存儲器(CGROM)已經存儲了160個不同的點陣字符圖形。這些字符包括:阿拉伯數字、英文字母的大小寫、常用的符號和日文假名等。每一個字符都有一個固定的代碼,比如大寫的英文字母“A”的代碼是0100_0001B(41H)。

顯示的時候,模塊把地址41H中的點陣字符圖形顯示出來,我們就能看到字母“A”。在編程實時,只需要輸入相應字符的地址,液晶屏就會輸出相應的字符。

FPGA對液晶模塊的寫操作、屏幕和光標的操作都是通過指令編程來實現的。1602型液晶的操作指令表如表10.4所示。

表10.4 1602型液晶模塊的指令表

序號 | 指令 | RS | RW | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

1 | 清顯示 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

2 | 光標返回 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | * |

3 | 光標或顯示模式 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | I/D | S |

4 | 顯示開/關控制 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | D | C | B |

5 | 光標或字符移位 | 0 | 0 | 0 | 0 | 0 | 1 | S/C | R/L | * | * |

6 | 功能設置命令 | 0 | 0 | 0 | 0 | 0 | DL | N | F | * | * |

7 | 字符發生器地址設置 | 0 | 0 | 0 | 1 | 字符發生器地址(AGG) | |||||

8 | DDRAM地址設置 | 0 | 0 | 1 | 顯示數據存儲器DDRAM的地址(ADD) | ||||||

9 | 讀忙標志或地址 | 0 | 1 | BF | 計數器地址(AC) | ||||||

10 | 寫數據到RAM | 1 | 0 | 要寫的數據 | |||||||

11 | 從RAM讀數據 | 1 | 1 | 讀出的數據 | |||||||

各條指令的說明如下(表10.4中,設1為高電平、0為低電平)。

·指令1:清顯示,指令碼01H,光標復位到地址00H位置。

·指令2:光標返回,光標返回到地址00H。

·指令3:光標和顯示模式設置。其中I/D表示光標移動方向,高電平右移,低電平左移;S表示屏幕上所有文字是否左移或者右移,高電平表示有效,低電平則無效。

·指令4:顯示開/關控制。其中D表示控制整體顯示的開與關,高電平表示開顯示,低電平表示關顯示;C表示控制光標的開與關,高電平表示有光標,低電平表示無光標;B表示控制光標是否閃爍,高電平閃爍,低電平不閃爍。

·指令5:光標或顯示移位。其中S/C表示高電平時移動顯示的文字,低電平時移動光標;R/L表示文字或光標的移動方向,高電平為右移,低電平為左移。

·指令6:功能設置命令。其中DL表示高電平時為4位總線,低電平時為8位總線;N表示低電平時為單行顯示,高電平時雙行顯示;F表示低電平時顯示5×7的點陣字符,高電平時顯示5×10的點陣字符。

·指令7:字符發生器RAM地址設置。

·指令8:DDRAM地址設置。

·指令9:讀忙信號和光標地址。其中BF表示忙標志位,高電平表示忙,此時模塊不能接收命令或者數據,如果為低電平表示不忙。

·指令10:寫數據。

·指令11:讀數據。

10.4.3VGA顯示接口的設計與實現

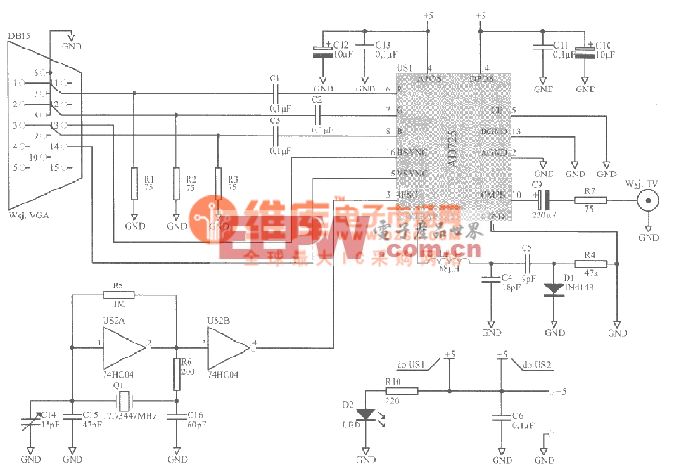

由于VGA接口是模擬信號,而FPGA只能支持數字信號,因此需要專用的D/A轉換芯片來實現模擬到數字的轉換。常用的DAC芯片有ADI公司的ADV7123或者ADV7125等。

在某些應用場合下,VGA顯示器僅僅是用來顯示文字符號或者簡單圖形,不需要豐富的色彩和細膩的畫面。這時候,VGA接口就可以適當地簡化。

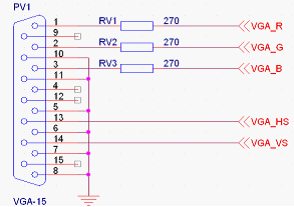

標準的VGA接口連接器為DB15,在15個管腳里面有5個是最重要的。它們分別是紅、綠,藍三基色信號和水平、垂直兩個同步控制信號,如圖10.18所示,其中,VGA_R、VGA_G、VGA_B、VGA_HS、VGA_VS是直接連接到FPGA的管腳。

圖10.18簡化的VGA接口電路連接

FPGA的管腳只有高電平和低電平兩種狀態,因此對于每個色彩分量信號也僅有兩種狀態。這樣3個色彩分量就可以組合出8種顏色,如表10.5所示。

表10.5 簡化的VGA接口色彩對照表

VGA_R | VGA_G | VGA_B | 對應的顯示顏色 |

0 | 0 | 0 | 黑色 |

0 | 0 | 1 | 綠色 |

0 | 1 | 0 | 藍色 |

0 | 1 | 1 | 藍綠色 |

1 | 0 | 0 | 紅色 |

1 | 0 | 1 | 品紅色 |

1 | 1 | 0 | 黃色 |

1 | 1 | 1 | 白色 |

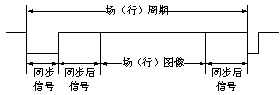

VGA信號如果要正常顯示,那么輸出信號必須滿足一定的時序關系。如圖10.19所示為VGA接口電路的通用時序關系。不同的分辨率和刷新率有不同的時序如表10.6所示。

圖10.19VGA接口電路的通用時序關系

表10.6 常見分辨率的VGA時序參數表

顯示模式 | 像素時鐘 /MHz | 水平方向(以像素計算) | 垂直方向(以行計算) | ||||||

有效視頻信號 | 同步前 | 同步信號 | 同步后 | 有效視頻信號 | 同步前 | 同步信號 | 同步后 | ||

640×48060Hz | 25.175 | 640 | 16 | 96 | 48 | 480 | 11 | 2 | 31 |

800×60060Hz | 40.000 | 800 | 40 | 128 | 88 | 600 | 1 | 4 | 23 |

1024×76860Hz | 65.000 | 1024 | 24 | 136 | 160 | 768 | 3 | 6 | 29 |

評論