利用FPGA實(shí)現(xiàn)外設(shè)通信接口之: 典型實(shí)例-RS-232C(UART)接口的設(shè)計(jì)與實(shí)現(xiàn)

10.6典型實(shí)例16:RS-232C(UART)接口的設(shè)計(jì)與實(shí)現(xiàn)

10.6.1實(shí)例內(nèi)容及目標(biāo)

1.實(shí)例的主要內(nèi)容

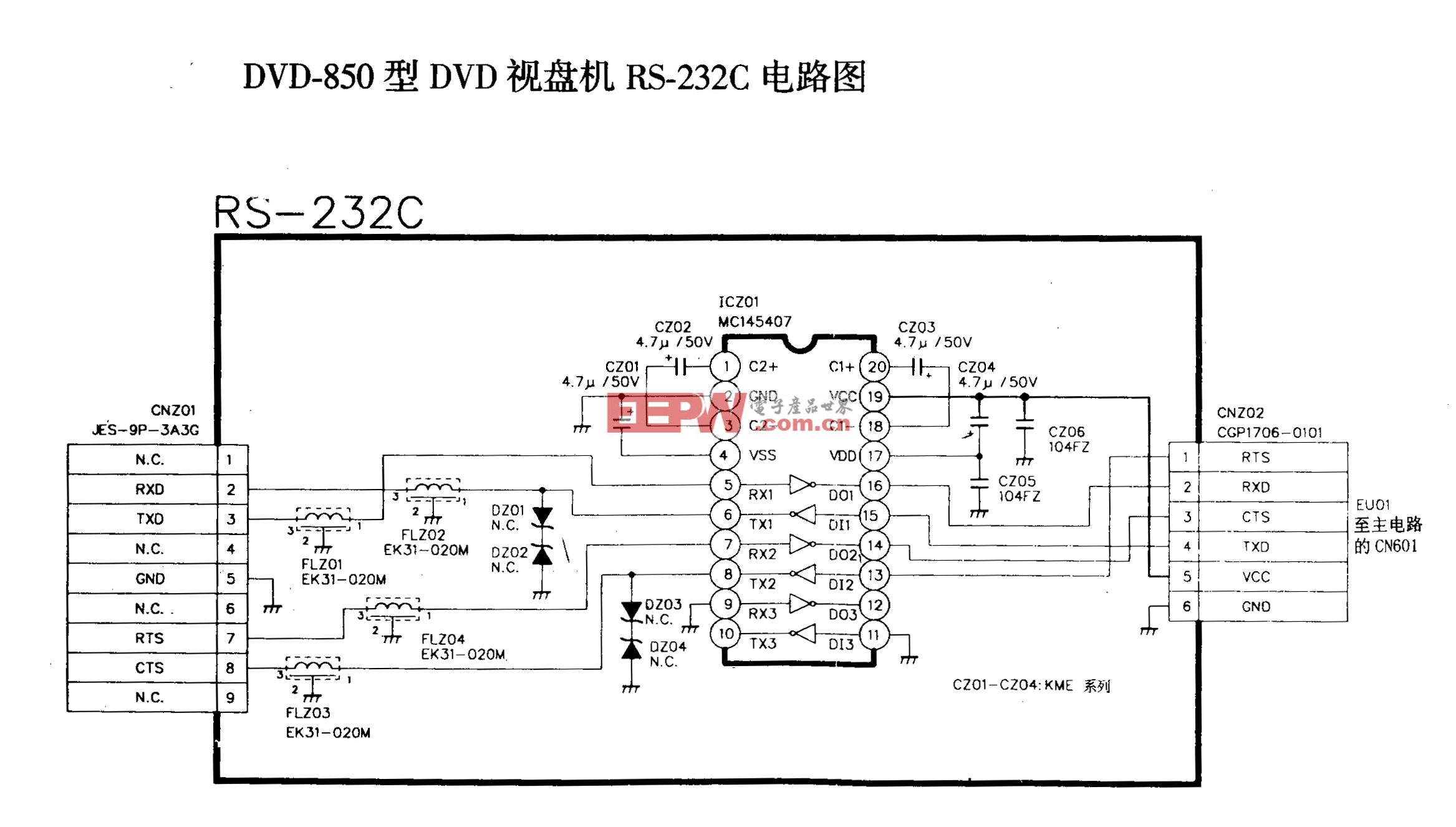

本節(jié)旨在通過分析UART控制器,設(shè)計(jì)實(shí)現(xiàn)了FPGA通過RS-232C接口與PC機(jī)的通信。設(shè)計(jì)過程中用Modelsim對UART控制器進(jìn)行仿真,幫助讀者進(jìn)一步了解UART協(xié)議的具體時(shí)序。

2.實(shí)例目標(biāo)

通過本實(shí)例,讀者應(yīng)達(dá)到以下目標(biāo)。

·了解UART工作原理和時(shí)序。

·熟悉Modelsim仿真的流程。

·熟練掌握狀態(tài)機(jī)的使用。

·實(shí)現(xiàn)FPGA與PC機(jī)之間的RS-232C接口通信。

10.6.2實(shí)例詳解

系統(tǒng)上電復(fù)位后,先將20個(gè)數(shù)寫入FPGA內(nèi)部資源BlockRam(可以用IP核來實(shí)現(xiàn)),然后根據(jù)設(shè)定的協(xié)議(該協(xié)議可自己設(shè)定)來建立PC機(jī)與FPGA的通信,此處設(shè)定的協(xié)議如下。

PC機(jī)要從串口讀取數(shù)據(jù)時(shí),先從串口發(fā)送E4H、00H。E4H代表FPGA的地址(可以隨意設(shè)定一個(gè)數(shù)),00H表示要讀取數(shù)據(jù)。FPGA收到這兩個(gè)數(shù)據(jù)后,通過串口給PC機(jī)反饋信號。發(fā)送E4H、E1H,表示FPGA已經(jīng)收到了PC機(jī)的命令,要開始向PC機(jī)發(fā)送數(shù)據(jù)。PC端準(zhǔn)備接收數(shù)據(jù),建立了此連接后,PC機(jī)可從FPGA讀出最初寫入BlockRam中的值了。

10.6.3BlockRAM的實(shí)現(xiàn)方法

對于BlockRam,可以直接應(yīng)用IP核來實(shí)現(xiàn),具體實(shí)現(xiàn)步驟如下。

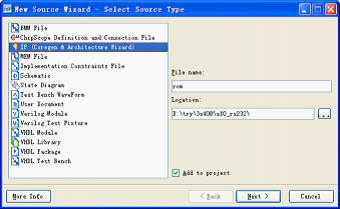

首先為工程添加新的設(shè)計(jì)文件,選擇“NewSource…”,如圖10.23所示。

圖10.23新建IP核設(shè)計(jì)文件

在彈出的對話框里面選擇創(chuàng)建IP(CoreGenArchitectureWizard)類型文件,并為該文件設(shè)置文件名及路徑,單擊“Next”按鈕,如圖10.24所示。

圖10.24選擇IP核類型

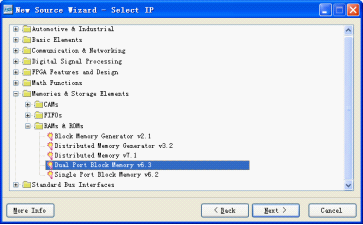

在選擇IP核類型對話框中選擇“DualPortBlockMemory6-1”,即可生成一個(gè)雙口RAM。單擊“Next”按鈕進(jìn)入雙口RAM設(shè)置向?qū)В鐖D10.25所示。

在該向?qū)е校獙υ撾p口RAM的屬性進(jìn)行設(shè)置。

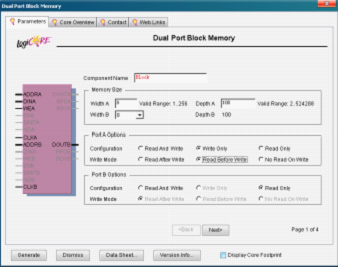

圖10.25雙口BlockMemory設(shè)置向?qū)?/p>

如圖10.25所示,WidthA、WidthB分別為寫入兩個(gè)口的數(shù)據(jù)的位數(shù),Depth為容量,在這里設(shè)為100,實(shí)際中只用到20個(gè)。對A口,上電復(fù)位后,就將20個(gè)數(shù)據(jù)寫入A口,因此A口設(shè)為WriteOnly,對于B口,F(xiàn)PGA向PC機(jī)發(fā)送數(shù)據(jù)時(shí)從B口讀取數(shù)據(jù),因此B口設(shè)為ReadOnly,設(shè)置完畢后單擊“Generate”按鈕即可。

10.6.4FPGA代碼的設(shè)計(jì)實(shí)現(xiàn)

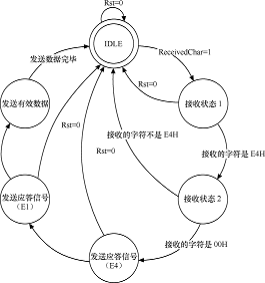

整個(gè)代碼采用了4個(gè)狀態(tài)機(jī)來實(shí)現(xiàn),其中兩個(gè)狀態(tài)機(jī)用于從串口讀取數(shù)據(jù),另外兩個(gè)用于向串口寫入數(shù)據(jù)。下面以從串口讀取數(shù)據(jù)為例來說明狀態(tài)機(jī)的工作過程。

從串口讀取數(shù)據(jù)的兩個(gè)狀態(tài)機(jī)主要完成如下功能:從串口接收到字符,并判斷是不是E4H、00H(自定協(xié)議規(guī)定的內(nèi)容),如果是,就給出Response(應(yīng)答)信號,通知發(fā)送數(shù)據(jù)狀態(tài)機(jī)開始向PC機(jī)發(fā)送數(shù)據(jù)。

這兩個(gè)狀態(tài)機(jī),一個(gè)為主狀態(tài)機(jī),用于連續(xù)從串口讀取數(shù)據(jù);一個(gè)為輔狀態(tài)機(jī),用于從串口讀取一個(gè)字節(jié)的數(shù)據(jù)。由于串口接收數(shù)據(jù)是一位一位地接收,該狀態(tài)機(jī)就控制從串口接收所有位,并將結(jié)果存入一個(gè)8位的寄存器。

當(dāng)輔狀態(tài)機(jī)接收到一個(gè)字符后,就給主狀態(tài)機(jī)一個(gè)Received_char信號。主狀態(tài)機(jī)判斷是不是E4H信號,如果是,就跳到下一個(gè)狀態(tài),等待輔狀態(tài)機(jī)接收下一個(gè)字符;如果下一個(gè)接收到的字符是00H,那么就給出Response信號。

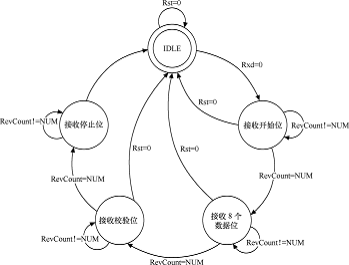

系統(tǒng)狀態(tài)圖如圖10.26所示。

圖10.26系統(tǒng)狀態(tài)圖

狀態(tài)機(jī)描述是一種非常好的方法,用戶可在此基礎(chǔ)上加以修改,用于自己的實(shí)際設(shè)計(jì)當(dāng)中。單個(gè)字符接收的狀態(tài)機(jī)如圖10.27所示。

圖10.27單字符接收狀態(tài)機(jī)

對于發(fā)送數(shù)據(jù)的兩個(gè)狀態(tài)機(jī),其工作機(jī)理與上面相同,不再贅述。詳細(xì)設(shè)計(jì)參考實(shí)例代碼。

10.6.5波特率的設(shè)定

串口通信必須要設(shè)定波特率。本設(shè)計(jì)中采用的波特率為9600kbit/s,采用的時(shí)鐘為50MHz,相當(dāng)于傳送一位數(shù)據(jù)需要約5028個(gè)時(shí)鐘周期。這里采用減法計(jì)數(shù)器來控制,即計(jì)數(shù)器計(jì)到5028個(gè)時(shí)鐘周期后,就開始傳輸下一位數(shù)據(jù)(也可以通過對時(shí)鐘分頻來實(shí)現(xiàn))。

10.6.6ModelSim仿真驗(yàn)證

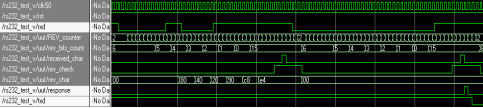

FPGA從串口接收數(shù)據(jù)仿真結(jié)果,如圖10.28所示。

圖10.28從串口接收數(shù)據(jù)仿真結(jié)果

rxd為模擬PC機(jī)發(fā)出的E4H、00H信號。從圖中可以看到,當(dāng)FPGA收到這兩個(gè)信號后,給出了Response脈沖。發(fā)送狀態(tài)機(jī)收到該信號后,給出txd的低電平信號,通知PC機(jī)要開始發(fā)送數(shù)據(jù)了。

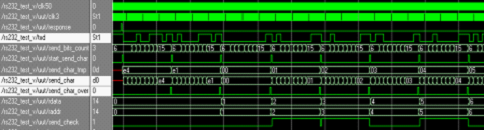

如圖10.29所示,txd為FPGA向PC機(jī)發(fā)送的數(shù)據(jù)。發(fā)送狀態(tài)機(jī)收到Response信號后,給出txd低電平信號,開始發(fā)送數(shù)據(jù)。先發(fā)送應(yīng)答信號E4H、E1H,之后開始發(fā)送開始寫入BlockRam的20個(gè)數(shù),從0~19。圖中raddr為BlockRam的地址,rdata為從BlockRam中讀取的數(shù)據(jù)。

圖10.29SDRAM控制器仿真結(jié)果

在仿真時(shí),為了顯示方便,沒有按照5028個(gè)時(shí)鐘傳輸一位,而是4個(gè)時(shí)鐘就傳輸一位。

10.6.7小結(jié)

本節(jié)對數(shù)字系統(tǒng)中常用的UART控制器做了初步的介紹,并在Modelsim中實(shí)現(xiàn)了對SDRAM控制器的仿真,最后通過編譯下載在紅色颶風(fēng)的開發(fā)板上實(shí)現(xiàn)了預(yù)定功能。

通過這個(gè)實(shí)例,讀者能夠掌握UART控制器以及RS-232C接口的設(shè)計(jì)實(shí)現(xiàn)方法,并學(xué)會(huì)將這個(gè)控制器集成到更為復(fù)雜的設(shè)計(jì)中去。

評論