利用FPGA實現外設通信接口之: 利用FPGA實現A/D、D/A轉換器接口

10.5利用FPGA實現A/D、D/A轉換器接口

10.5.1A/D、D/A轉換器接口的特點

A/D、D/A轉換器是FPGA系統設計中的常用器件,經常用來實現模擬信號和數字信號的相互轉換。根據應用場合的不同,A/D、D/A轉換芯片的性能指標參數差別比較大,因此接口格式也無法統一。

本文引用地址:http://www.104case.com/article/201706/348805.htm10.5.2A/D、D/A轉換器接口的實現方法

1.標準接口的A/D、D/A轉換器與FPGA的接口設計

在一些典型的應用領域,需要處理的信號單一,芯片廠家設計的芯片一般會遵循一些行業標準接口。例如音頻信號處理領域,很多廠家的音頻A/D、D/A轉換芯片都支持SPI接口。

FPGA實現這些標準的接口,如SPI接口,可以通過網絡或者FPGA廠家獲得一些參考代碼。FPGA芯片的生產廠家會在其開發工具軟件里面集成一些常用接口的IP核,設計者可以免費使用,降低了開發難度。

另外,有一些開源的網站,如http://www.opencores.org等,也提供了免費的接口IP核的源代碼下載服務。設計者可以下載代碼后,經過仿真驗證或者適當修改后,應用到自己的系統中去。

2.特殊接口的A/D、D/A轉換器與FPGA的接口設計

還有很多信號處理領域,如通信系統設計領域,需要處理的信號很復雜。這種情況下,A/D、D/A的芯片廠家一般會根據處理的精度和采樣的速度要求來設計接口時序。

設計者要根據廠家提供的芯片手冊給出的時序來設計接口。

有些高速的A/D或者D/A芯片會采用LVDS差分信號電平標準。這樣的情況下,FPGA的管腳也要采用對應的LVDS模式。

需要注意的是,FPGA上每一組LVDS管腳是成對出現的,不是任意分組的。而且,如果一個BANK被設定為LVDS,那么這個BANK的所有管腳都是LVDS模式的。

10.5.3AD/DA轉換器接口的注意事項

1.選擇正確的時鐘采樣邊沿

對于一個邊沿采樣的數據采集模塊,經常需要確定采用上升沿還是下降沿來采樣數據。那么,選擇的依據就是保證數據采樣的穩定、可靠。

為了保證同步,FPGA的采樣時鐘一般采用A/D轉換芯片的輸出時鐘,這個時鐘和數據是同步的。這個時鐘和數據的關系與A/D轉換芯片的具體型號有關。

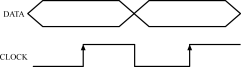

圖10.20A/D芯片的部分輸出信號時序關系

例如,在如圖10.20所示的時序圖中,每當時鐘的上升沿數據產生變化。那么這樣的情況下,在時鐘的下降沿的時候,數據是最穩定的,適合采樣。

2.選擇適合的同步頭檢測方法

A/D芯片的輸出數據一般都是打包數據,以數據幀的格式輸出。數據幀的同步格式分為兩種:外同步模式和內同步模式。

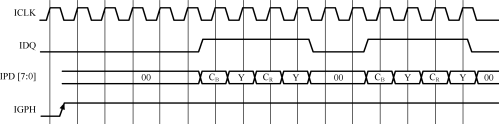

圖10.21A/D芯片的部分輸出信號時序關系

外同步模式:是指除了時鐘和數據信號外,還有同步指示信號。同步指示信號可以是脈沖信號,指示一幀有效數據的開始;也可以是電平信號,指示一幀有效數據的持續時間。

內同步模式:是指輸出信號中只有時鐘和數據信號,同步頭隱藏在數據之中,如表10.7所示是ITU656標準的數字視頻信號。

表10.7 ITU656標準的數字視頻信號

幀結構 | ||||||||||||

BlankingPeriod | … | 80 | 10 | |||||||||

TimingReferenceCode | FF | 00 | 00 | SAV | ||||||||

720PixelsYUV4:2:2Data | Cb0 | Y0 | Cr0 | Y1 | Cb2 | Y2 | … | Cr718 | Y719 | |||

TimingReferenceCode | FF | 00 | 00 | EAV | ||||||||

BlankingPeriod | 80 | 10 | … | |||||||||

其中,“FF0000EAV”和“FF0000SAV”就是幀同步頭,其作用也是用來指示有效數據開始和結束。其格式為:“FF0000XY”,XY的定義如下。

SAV_EVEN=8H80

EAV_EVEN=8H9D

SAV_ODD=8HC7

EAV_ODD=8HDA

3.選擇有效的緩存策略

在數據采集系統中,緩存結構的設計直接影響系統的性能。對于簡單的設計,可以采用一個FIFO或者雙口RAM來實現緩存。如果單緩存不能滿足系統的性能要求,可以采用乒乓結構的緩存。

在有些特殊情況下,采集模塊后面數據處理模塊的處理時間不固定,和數據內容相關。這時候采用乒乓結構的緩存策略就不能滿足要求了,因為乒乓結構的切換時間一般是固定的,而且和數據內容是無關的。

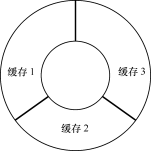

還有一種比乒乓結構更復雜的緩存管理策略,那就是三緩存環形結構。如圖10.22所示,這樣的結構雖然比乒乓結構提供了更好的緩存性能,但是管理的復雜度大大提高了,系統的延遲也增加了。

圖10.22三緩存的環形緩存區示意圖

無論是單緩存,雙緩存還是三緩存結構,只要能滿足系統的實時采集要求就是有效的緩存策略。

評論