自變模無線電能傳輸全數字鎖相環

2 仿真實驗及實物驗證

本文引用地址:http://www.104case.com/article/201705/359756.htm根據系統各部分電路的功能要求,該文采用Verilog HDL語言和自頂向下的系統設計方法,對ADPLL電路進行綜合設計。并分別利用QuartusⅡ 15.1和ModelSim-Altera 10.4b軟件對源程序進行了功能和時序仿真,利用Signal Tap Ⅱ觀察設計的內部信號波形。

例如,根據滯后環節的功能要求,我們用Verilog設計了滯后環節的硬件電路,其部分Verilog設計程序如下:

module chaoqianzhihou_1(clk_1,rst_n,fout,fout_1);

input clk_1,rst_n,fout;

output fout_1;

wire fout,fout_pos,fout_neg,count_onetozero;

reg fout_1;

reg fout_this,fout_last;

reg [15:0] count_last,count_this;

reg [15:0] count;

assign fout_pos=(fout_last==0 && fout_this==1) ? 1:0;

assign fout_neg=(fout_last==1 && fout_this==0) ? 1:0;

assign count_onetozero=(count_last==1 && count_this==0) ? 1:0;

在仿真圖中,clk為50MHz的系統時鐘,rst_n為復位信號,U0為鎖相環輸入信號,fout為鎖相環輸出信號,A的值決定鎖相環處在不同捕捉區域,及對應的比例積分系數K1、K2的大小,因為積分系數一定時,比例系數越小,則系統穩定性越好,鎖相速度越快,但太小會導致系統對輸入噪聲過于敏感;比例系數一定時,積分系數越小,則系統響應速度越快,但穩定裕度越小,且輸出相位出現震蕩[3]。圖4比較了不同環路濾波器參數對該文提出的ADPLL動態性能的影響。所以當相位誤差大于輸入信號周期的1/8時為快捕區,在輸入信號周期的1/8到1/16之間為慢捕區,小于輸入信號周期的1/16為鎖定區,比例系數依次為1/2、1/4、1/8,積分系數依次為1/256、1/512、1/1024。通過上述設置可實現自動變模控制。

圖5為鎖相過程中,濾波器自動變模模塊的仿真波形圖。在輸入信號突然發生變化時,前4個輸入周期A為10屬于快捕區,第5個周期A為01屬于慢捕區,第6個周期A為00屬于鎖定區。

圖6為加入超前、滯后模塊后輸出信號超前輸入信號15個機器周期的仿真波形圖。

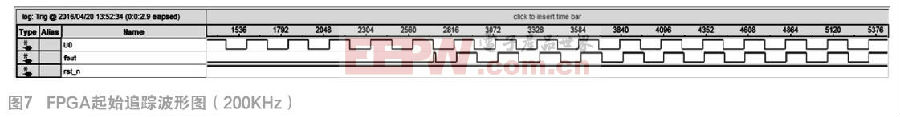

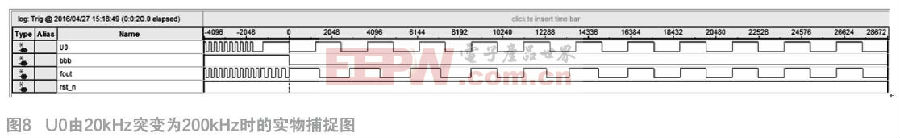

圖7、圖8為EP4CE6E22C8型器件基于Signal Tap Ⅱ實現的全數字鎖相環實測波形圖。

3 結論

該文提出基于FPGA的自適應變模控制無線電能傳輸全數字鎖相環,該ADPLL采用比例、積分結構且比例、積分系數可調,使該ADPLL鎖相速度加快,超調量減小,通過中心頻率可變分頻器,使鎖相范圍增大。當系統時鐘為50MHz時,該鎖相環的鎖相范圍為1kHz-1MHz,該鎖相環環路失所時的重新鎖定時間最長為10個輸入信號周期。通過參數設置可調節輸出信號的相位。本文使用modelsim仿真并用Signal Tap Ⅱ觀測實物波形,理論與實踐一致。適用于無線電能傳輸電源對負載頻率跟蹤的需要。

參考文獻:

[1]楊慶新,張獻,李陽.無線電能傳輸技術及其應用[M].北京:機械工業出版社,2014.

[2]趙彪,陳希有,于慶廣.用于非接觸電能傳輸的自適應諧振技術原理[J].電工電能新技術,2010,29(2):33-37.

[3]盛臻.快速自適應全數字鎖相環的研究與設計[D].南華大學,2014.

[4]肖帥,孫建波,耿華,等.基于FPGA實現的可變模全數字鎖相環[J].中國電機工程學報,2012,27(4):153-158.

[5]胡華春,石玉.數字鎖相環路原理與應用[M].上海:上海科學技術出版社,1990.

本文來源于《電子產品世界》2017年第6期第58頁,歡迎您寫論文時引用,并注明出處。

評論