效率最好的內存測試電路開發環境

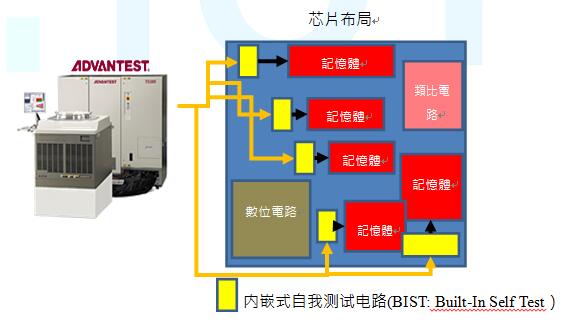

1.概述:整合性內存自我測試電路產生環境-Brains

本文引用地址:http://www.104case.com/article/201702/343955.htmBrains是從整體的芯片設計切入,利用硬件架構共享的觀念,可以大幅減少測試電路的門數 (Gate Count),并且讓使用者能輕易產生優化的BIST電路。Brains可以自動的判讀內存并將其分群 (Grouping),從產品設計前端大幅提升測試良率、降低測試成本,提高產業競爭力。Brains的五級到七級的彈性化管線式架構,可以滿足快速內存測試的需求,目前最高測試的速度已經可以達到1.2GHz,整體BIST電路的門數平均只需200個門數。另外為了簡化嵌入內存測試電路的復雜度,Brains只需簡單步驟即可完成內存測試電路的設計與嵌入。Brains的先進功能可以大幅縮減DPPM與降低芯片測試成本進而降低整體芯片成本,增加產品的可靠度以及增加產品的競爭力。

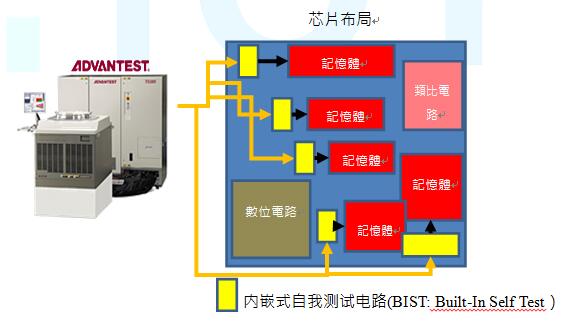

圖1-1. 傳統BIST示意圖

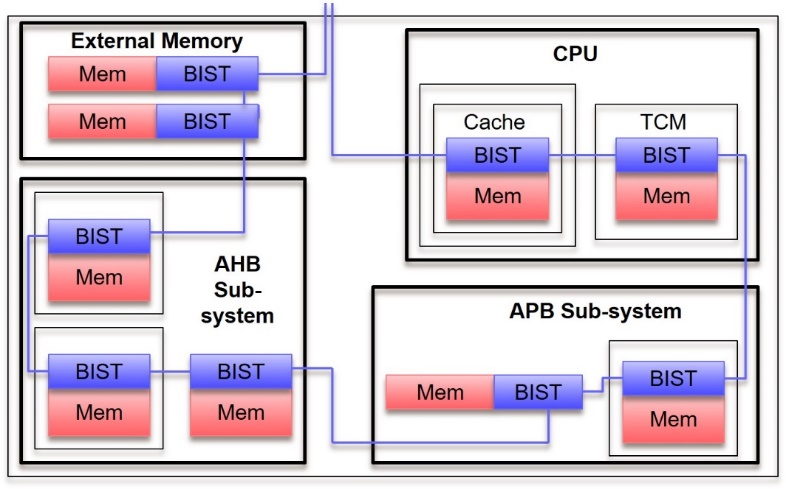

圖1-2. 傳統Memory Testing解決方案

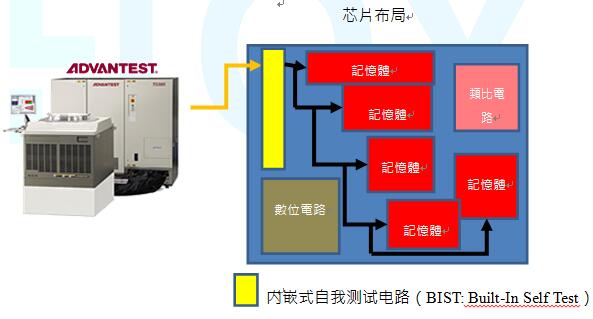

圖1-3. 厚翼科技的BIST示意圖

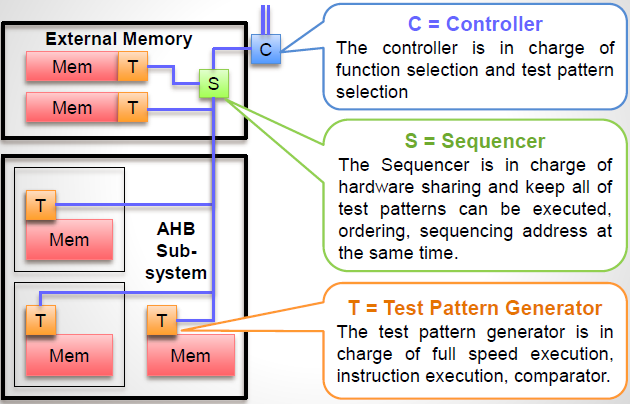

圖1-4. 厚翼科技的解決方案

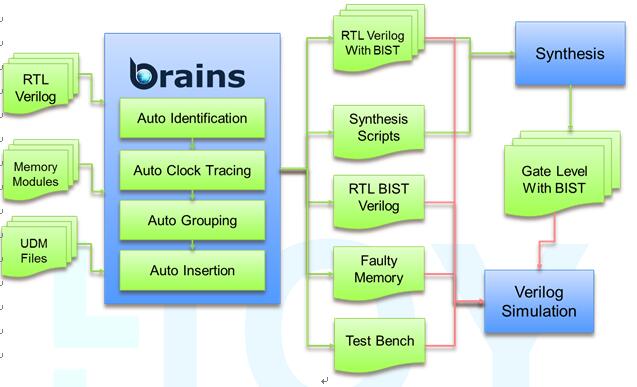

2. Brains架構

Brains是一個內存測試電路整合性開發環境,基本架構圖如下:

圖2-1. BRAINS執行架構圖

Brains 輸入檔:

RTL Verilog : 包含memory models 的Top HDL design檔案

Memory Modules : Memory models verilog檔案

UDM Files : 用戶自定義內存檔案

Brains 輸出檔:

RTL Verilog with BIST : 整入BIST電路的top HDL design檔案

Synthesis Scripts : 合成相關scripts檔案

RTL BIST Verilog : BIST 電路verilog檔案

Fault Memory : 整入error bit之memory models

Test Bench : 供BIST 電路仿真用之Testbench

3. 功能描述

BRAINS有下列功能:

n 支持RTL和Gate-level格式

n 透過BFL (Brains Feature List)設定BRAINS的功能

n 自動進行內存判別

n 自動產生Testbench

n 自動嵌入 BIST到原設計

n 自動追蹤 Cock Source

n 透過UDM (User Defined Memory) 檔案支持用戶自行定義的內存

4. 實作流程

Brains實作支援Top-down Flow和Bottom-up Flow,以下針對Top-down Flow加以介紹。

Brains BFL Flow – Top-down Flow

本章節介紹如何透過BFL檔案,并搭配Top-down 流程,來產生相對應之BIST電路。本章節提及之example case及相關文件,使用者若有需求,可與厚翼科技聯絡,進行索取。

4.1 解壓縮 Example Case

unix% tar xvfz multi_lab.tgz

unix% cd multi_lab/top_down_lab

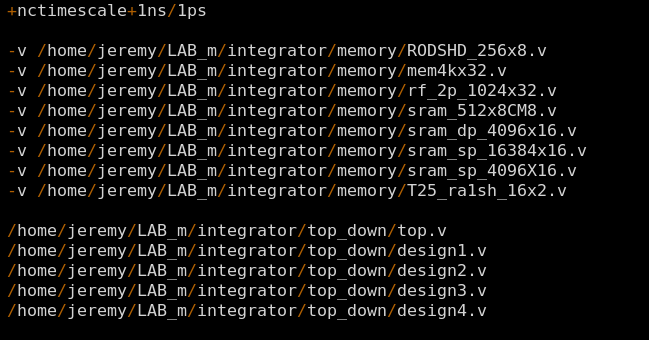

4.2 建立 File-List 檔案 (*.f file)

完整的File-List 檔案可讓Brains 的執行更加順利,完整的File-List 檔案包含design verilog 檔案所使用的memory model 檔案,相關的standard cell 和macro檔案如下:

n Design.v (RTL or netlist)

n Memory.v

n Standard_cell.v (when your design is netlist)

n Parameter, e.g. +define+、+incdir+PATH/DIR …

圖4-1為 run.f 檔案之范例,用戶可依照此格式來產生相對應的File-List 檔案。

圖4-1. run.f 檔案范例

4.3 其它輸入檔案

n 如果使用者有特殊grouping需求,則可提供相關輸入檔案。如:*.def檔案或*.meminfo 檔案。*.def檔案可讓Brains依據實際memory model 擺放位置來做grouping。*.meminfo 檔案則可讓Brains依據使用者想要的grouping架構來執行。

n Memory model library檔案:此檔案可讓Brains依據其中所定義之power數值,來做為grouping的條件。

4.4 Memory Model 檢查功能 (Optional)

Brains 可幫助使用者識別出design 中所包含的memory model。用戶可使用memchecker 指令來檢查所使用到的memory models。詳細執行流程請參考Brains quick start guide文件,附錄A。

如果design中有memory model無法自動被Brains識別出來時,使用者可自行編寫 UDM 檔案,該檔案用來描述memory models 相關腳位及讀寫行為。詳細定義請參考brains_udm_ug.pdf文件。

評論