基于FPGA的高精度頻率電壓轉換系統設計實現

摘要 設計了一種線性F/V轉換系統。傳感器輸出的脈沖頻率信號經信號調理電路調理后輸入FPGA,FPGA測量脈沖信號的頻率,根據系統精度要求,需設計Q格式定點運算,測得的頻率經FPGA定點運算后得到與頻率大小成線性關系的D/A轉換的數字量,控制串行DAC7551輸出相應的電壓值。實驗結果表明,系統的轉換精度優于0.1%,改變系統的設計參數可實現更高精度的頻率信號到電壓信號的轉換。

本文引用地址:http://www.104case.com/article/201610/308499.htm關鍵詞 F/V轉換;精度;FPGA;Q8定點運算;DAC7551

脈沖型流量傳感器是流量儀表中一類主要的流量傳感器,如渦輪流量傳感器、渦街流量傳感器、遠傳型容積式流量計等。這類傳感器需將被測參數轉化為電模擬量顯示出來。頻率電壓轉換器作為一種功能器件,在測量儀器、自動控制、遙感遙測以及信號傳輸各個領域都有著廣泛的應用。傳統的F/V轉換器多采用模擬電路或單片機實現。采用模擬電路設計的F/V轉換器多采用如LM331、AD650等實現頻率信號到電壓信號的轉換,設計的系統具有轉換精度不高、待測頻率范圍固定、誤差較大的缺點;單片機設計的F/V轉換系統雖然有一定程度的改善,但由于自身測頻基準時鐘頻率的限制,仍然無法滿足高精度轉換的要求。本文根據系統要求:流量傳感器輸出的脈沖信號頻率范圍10~3 000 Hz,輸出模擬電壓信號范圍0~5 V,精度優于0.1%。采用FPGA實現脈沖信號頻率的測量,設計的系統滿足要求。

1 系統分析

F/V轉換的誤差主要存在于計數測量信號周期時的誤差、運算時的截位誤差和D/A變換器的量化誤差等。

首先考慮測量周期的誤差:選擇最大頻率信號3 000 Hz,其周期為333.3μs,0.1%誤差是333.3 ns。選用12 MHz時鐘作為時基信號,周期測量誤差為83.33 ns,對應83.33×5×0.1%/333.33=1.3 mV,誤差余量為3.7 mV。

M位D/A轉換器的誤差為5 000/2(M+1)mV,所以M只需>10位就可以滿足精度要求,考慮到D/A自身的誤差,可以選擇12位以上且INL1 LSB的D/A,以保證轉換精度。

輸入的頻率信號最小為10 Hz,所以最大計數值為1 200 000,需要21位長的計數器。

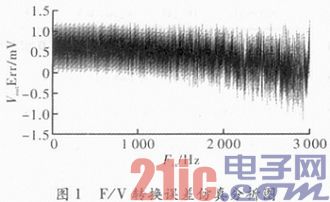

考慮截位誤差,使用Matlab仿真,得到使用12 MHz計數頻率12位D/A時,需要使用Q8定點運算才能保證系統精度,誤差曲線如圖1所示。使用Q8格式作定點運算時只需先將數據轉換為Q8定點數,然后進行計算,最后將結果轉換回一般格式即可(Q格式:小數點位于第n位元之右側,稱為Qn格式)。

2 系統總體結構

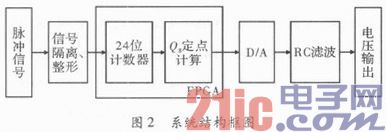

系統整體結構如圖2所示。FPGA測量經隔離整形后的脈沖信號的頻率,經Q8定點運算、截位等處理后得到D/A轉換的數字量,D/A輸出的電壓信號經RC濾波后得到最終與輸入脈沖頻率大小成線性關系的電壓信號。由于流量傳感器輸出的脈沖信號頻率可能會在10~3 000 Hz范圍連續變化,不一定是固定值,為保證系統轉換精度,利用FPGA計數連續兩個待測脈沖上升沿間的時基脈沖個數的方法得到脈沖信號的周期,周期的倒數即為脈沖信號的頻率。對固定頻率的測量較為簡單,本文主要討論對變化頻率的測量,系統可用于對固定頻率的測量。由于FPGA對待測脈沖信號的處理時間遠小于待測脈沖信號的周期,所以在下一個脈沖到來之前,FPGA已經完成對前一個脈沖的處理。

3 系統電路設計

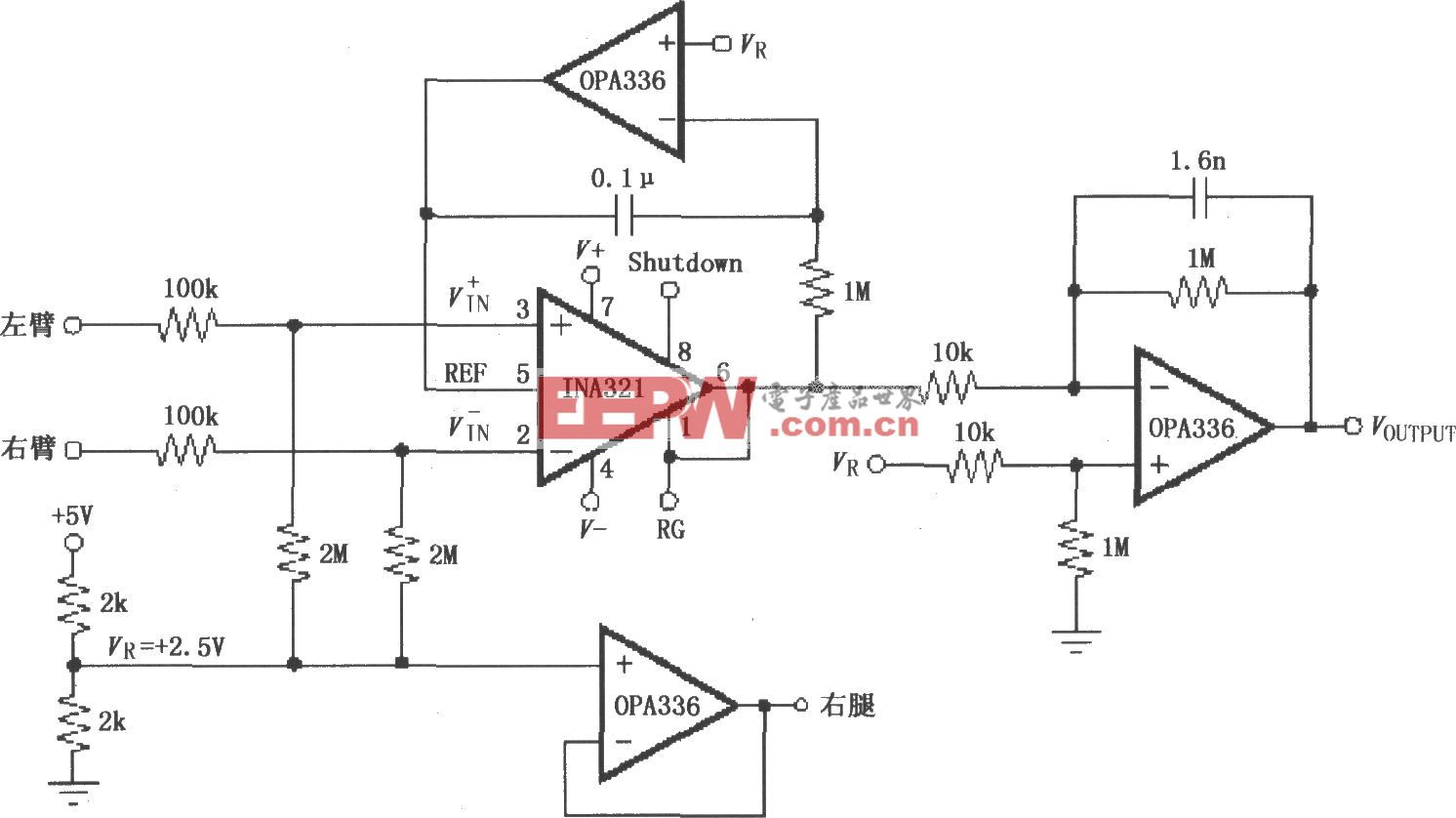

3.1 信號調理電路

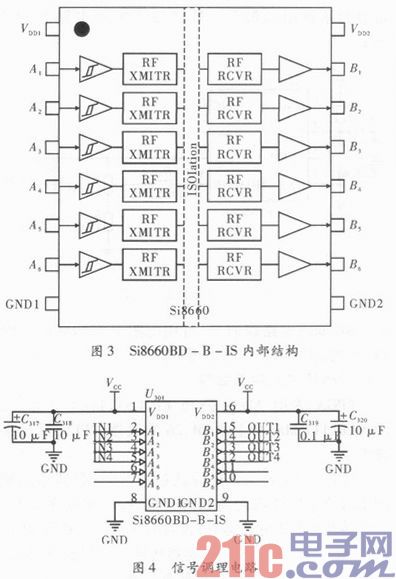

為保障系統對信號源的抗干擾能力,傳感器輸出的脈沖信號需經光電隔離并整形后再送入FPGA處理。信號調理芯片采用Silicon Labs的低功耗6通道數字隔離器Si8660BD—B—IS,可實現多路信號同時處理,它具有抗電磁干擾能力強、功耗低、隔離電壓高、壽命長的特點,且具有施密特整形電路的功能。其內部電路如圖3所示,信號調理電路如圖4所示。

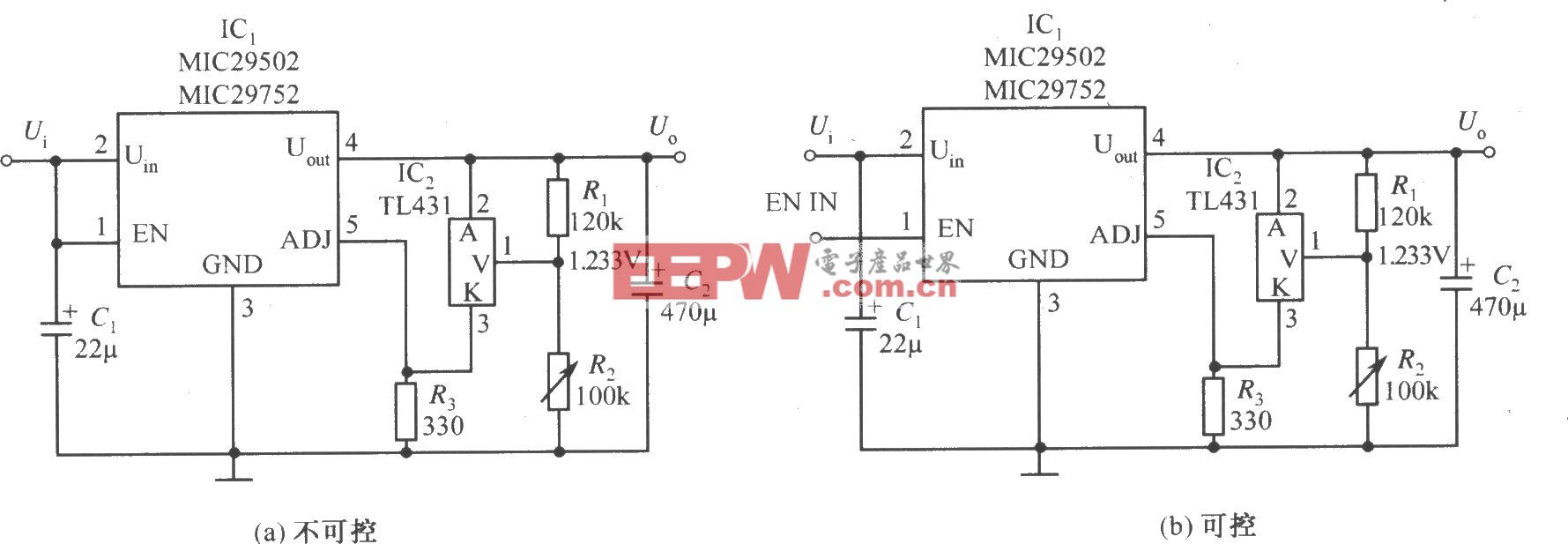

3.2 D/A轉換電路

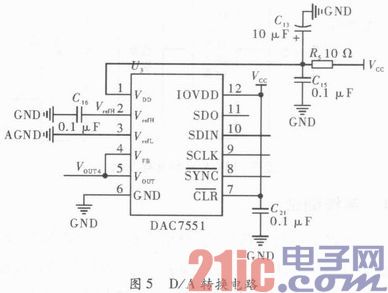

數模轉換器是一種數字和模擬混合信號處理電路。D/A轉換芯片采用串行DAC7551,+5 V電源供電,12 bit精度,INL為±0.35 LSB,軌至軌電壓輸出,輸出電壓建立時間最大為5μs,輸出電阻1Ω,滿足系統要求。設計的D/A轉換電路如圖5所示。

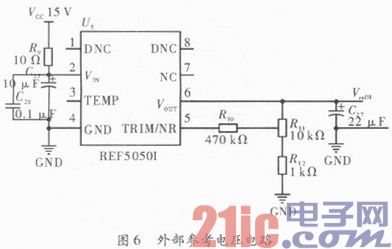

3.3 外部參考電壓電路及RC濾波電路

出于對精度及穩定性的要求,希望參考電壓源盡量對供電電源電壓和工藝參數以及芯片的工作溫度是相對獨立的。Ref5050為BB公司生產的高精度+5 V輸出穩壓模塊,最大溫度漂移為8×10-6/℃,輸出最大誤差電壓為輸出總電壓的0.1%,輸入電壓范圍為5.2~18 V,輸出電流范圍為±10 mA,常作為電路中的基準電壓源。外部參考電壓電路如圖6所示。

RC濾波電路較簡單,可用電阻電容構成的一階RC濾波電路即可,在此不再贅述。

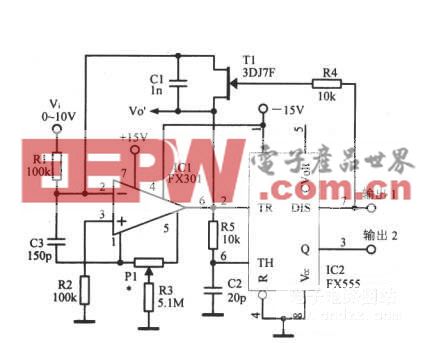

3.4 FPGA內部電路結構

FPGA選用Altera公司EP2C5T144C8 芯片,5000LE、117 kbit片上RAM、26乘法器、2PLL,滿足系統需求。

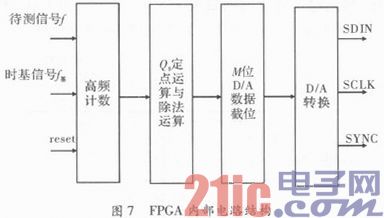

FPGA的主要工作是除法運算,當計數器給出被測信號單個周期內的高頻時鐘數N,取預存在FPGA中的轉換系數做除法運算;再對除法的結果值作M位截位,送外部M位D/A轉換器轉換,則得到相應的電壓值。FPGA內部電路結構如圖7所示。

4 系統測試

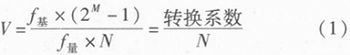

選擇高頻時基信號f基對輸入信號f的周期計數,得到計數值N,依據線性轉換關系,得到F/V的轉換如式(1)所示。式中,M是外部D/A轉換器的位數,f量是輸入脈沖信號的量程即3 000 Hz。

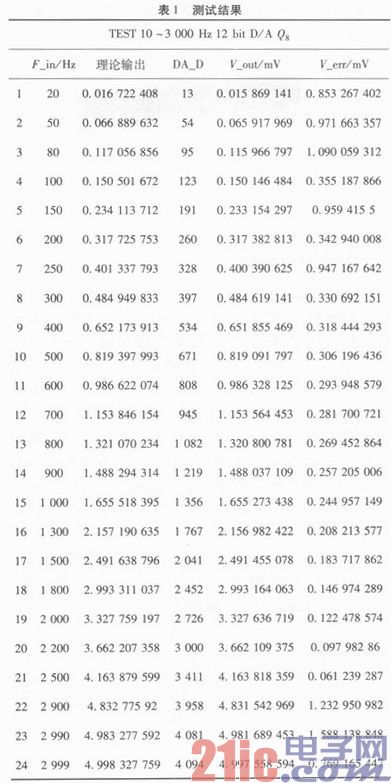

根據式(1)得到的測試結果如表1所示。輸入脈沖信號頻率范圍10~3 000 Hz,D/A芯片采用DAC7551,12 bit精度,采用Q8定點運算保證轉換精度。

5 結束語

目前在測量領域,脈沖信號既可作為已知的激勵信號,又可作為未知的被測信號。作為未知的被測信號,對其參數測試越顯重要。文中設計的F/V轉換器采用以FPGA為核心的模塊化設計方法,具有測試參數靈活配置、硬件電路簡單、容易實現、測頻范圍寬、轉換精度高等特點。根據系統需求,可靈活配置系統的參數。增加時基頻率、選用精度更高的D/A轉換芯片、增大Q運算的階數都可以實現更高精度的F/V轉換。與傳統實現方法相比,靈活性、測頻精度、轉換精度都得到了大幅提升。

評論