UltraScale架構(gòu)DDR4 SDRAM接口的秘密

Adrian Cosoroaba和Terry Magee在本月MemCon上給出了關(guān)于DDR4 SDRAM接口的詳細(xì)展示,該演示應(yīng)用于賽靈思UltraScale All Programmable FPGA上。接口設(shè)計(jì)將DDR SDRAM提升至2400Mbps甚至以上,同時(shí)降低接口功耗。為了達(dá)到這個(gè)目標(biāo),賽靈思的工程師們必須將DDR4接口問(wèn)題放在首位。除了設(shè)計(jì)將DDR4兼容UltraScale I/O PHY,他們從頭設(shè)計(jì)了DDR4 I/O PHY,然后擴(kuò)展它的性能并支持其他I/O的需求。結(jié)果:基本的13位可編程字節(jié)通道,這首先是一個(gè)DDR4 PHY。

本文引用地址:http://www.104case.com/article/201610/308425.htm如果你來(lái)自SoC的世界,也許不太明白為什么賽靈思需要選擇這樣做。因?yàn)楫?dāng)有成千上萬(wàn)甚至百萬(wàn)個(gè)邏輯單元和觸發(fā)器、幾兆的塊RAM和數(shù)千個(gè)DSP片時(shí),由于物理封裝的限制只有數(shù)百個(gè)I/O管腳,所以,I/O管腳是稀缺資源。所以,I/O管腳必須可編程且足夠靈活,可覆蓋任何可能的I/O使用范圍,從DDR4-2400 SDRAM驅(qū)動(dòng)庫(kù)到使LED閃爍以及其他更多的事情。這就是賽靈思為何如此做的原因。對(duì)于UltraScale架構(gòu)的FPGA來(lái)說(shuō),我們首先實(shí)現(xiàn)了I/O設(shè)計(jì)的難點(diǎn)——DDR4 PHY,然后再添加一些簡(jiǎn)單的。

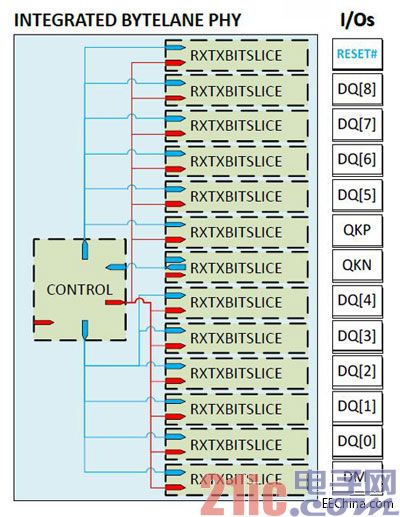

結(jié)果非常明顯,I/O字節(jié)通道架構(gòu)看來(lái)如此:

UltraScale FPGA I/O字節(jié)通道架構(gòu)

邏輯上下一個(gè)問(wèn)題也許是:“為什么13位?”簡(jiǎn)單的答案是,兩個(gè)這樣的庫(kù)涵蓋26位,這是DDR4 命令和地址行要求的。數(shù)據(jù)行、頻閃和預(yù)選要求每個(gè)字節(jié)各另外添加11位,這符合新的13位UltraScale I/O庫(kù)。. QDR和RL3 DRAM要求12個(gè)I/O行(9個(gè)數(shù)據(jù)行和2個(gè)時(shí)鐘),這也符合13位塊結(jié)構(gòu)。任何余下的關(guān)鍵都可編程另作他用。

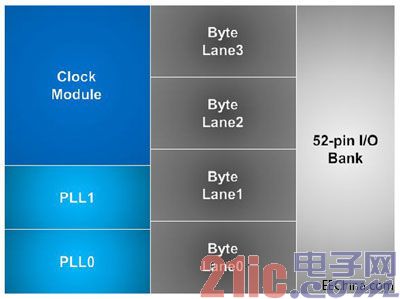

UltraScale FPGA的52管腳I/O庫(kù)封裝4個(gè)13位字節(jié)通道以及兩個(gè)PLL和一個(gè)時(shí)鐘模塊,看似如此:

一個(gè)UltraScale 52管腳IO庫(kù)

兩個(gè)PLL允許你將個(gè)庫(kù)分開(kāi),這樣就能在你的設(shè)計(jì)里為兩個(gè)完全不同的目標(biāo)服務(wù)。

評(píng)論