基于FPGA的導航抗干擾接收機數字變頻的實現

摘要 根據衛星信號結構、頻率特征設計和實現了導航抗干擾接收系統中,基于軟件無線電的上下變頻模塊。根據系統的A/D采樣頻率與轉換位數、阻帶衰減要求、頻率選擇性、增益,輸入輸出頻率在Matlab中建模。確定了DDC和DUC的設計方案,并在硬件上實現,重點是NCO和濾波器組設計,包括梳狀濾波器、半帶濾波器和補償濾波器。構建完成系統后進行了仿真驗證,可滿足系統設計要求。

本文引用地址:http://www.104case.com/article/201610/308419.htm導航接收機作為衛星導航系統的主要組成部分,是市場大規模和產業化的核心環節。研究導航接收機關鍵技術,對建設我國有自主知識產權的衛星導航接收系統有具有現實意義。因此,對用戶端接收機、拓寬應用范圍是GNSS研究的熱點。同時衛星導航信號弱、易受干擾會直接影響衛星導航系統在復雜干擾環境下發揮的作用。因此需研制具有抗干擾能力的接收系統。本文主要根據衛星信號結構、頻率特征設計了導航抗干擾接收系統中基于軟件無線電的上下變頻模塊。

1 DDC和DUC的系統設計

導航抗干擾系統中的數字接收機所采用的是數字混頻正交變換,但該方法在高采樣率時,混頻后端的濾波器需要較高的濾波器階數,對硬件資源的要求高,導致使用資源過多、功耗過大等問題。因此在實際的上下變頻技術應用中,多速率信號處理濾波器組常選擇CIC積分梳狀濾波器級聯HB半帶濾波器、級聯補償FIR濾波器的組合結構,來滿足設計要求。

1.1 設計指標

開發工具采用Xilinx公司的ISE,芯片采用Xilinx公司的FPGA—spantan3E。數字中頻信號中心頻率為70 MHz,帶寬為20 MHz,采樣率為90 MHz,濾波器阻帶衰減60 dB。下變頻中,經NCO提供的20 MHz本振信號混頻到零頻上,完成4倍的抽取。上變頻經過4倍插值,混頻到70 MHz中頻上,采樣率由22.5 MHz升至90 MHz。

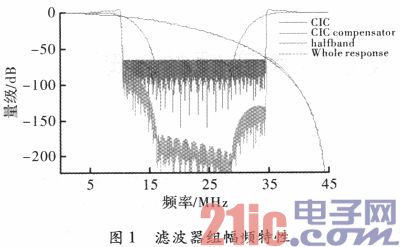

1.2 建立DDC和DUC設計方案

首先在Matlab中進行建模,確定濾波器組參數,包括濾波器級數、系數等。濾波器組方案采用2倍多級CIC濾波器抽取,級聯2級抽取半帶濾波器,最后級聯多級補償FIR濾波器。由此確定半帶濾波器和補償濾波器的系數和級數,幅頻特性如圖1所示。

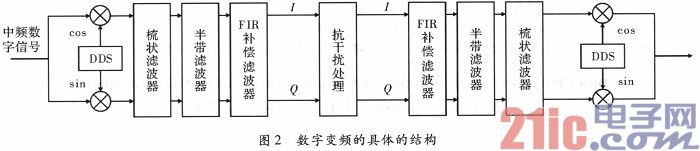

由此可得出設計的數字下變頻結構如圖2所示,包括數控振蕩器NCO模塊、數字混頻器模塊、CIC濾波器模塊、HB半帶濾波器模塊和FIR補償濾波器模塊。數字上變頻結構是數字下變頻的逆過程,兩者的工作原理、結構和實現互相對應。

1.3 DDS的設計

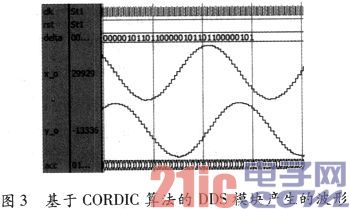

為避免使用大容量存儲器,可以考慮利用算法來產生正余弦樣本。CORDIC算法是一種基于矢量旋轉的坐標計算方法。該算法的基本思想是通過一系列固定的、與運算技術相關的角度不斷偏擺以逼近所需的旋轉角度。它有線性的收斂域和序列的特性,只要迭代次數足夠,即可保證結果有足夠的精度。當輸入90MHz的基準時鐘,步進字設為954 437 176(十進制),將輸出2 MHz的正余弦離散波形,圖3所示為DDS模塊在Modelsim中仿真結果。

與使用ROM查找表法相比,CORDIC算法產生DDS的優勢有:(1)所有運算都可通過移位和加減運算實現,無需耗費硬件乘法器資源,易于實現。(2)可使用循環迭代方法,節約硬件資源。(3)可通過流水線法,提高工作頻率。

1.4 濾波器組的設計

CIC濾波器的結構簡單,沒有乘法器,只有加法器,積分器和寄存器,適合工作在高采樣率。而且,CIC濾波器是一種基于零極點相消的FIR濾波器,實現上減少了復雜度與資源消耗,已被證明是在高速抽取或插值系統中的有效單元。

單級CIC濾波器的傳遞函數為

單級CIC濾波器旁瓣電平較大、阻帶衰減較差、降低旁瓣電平,可以采用多級CIC濾波器級聯的方法實現。根據Matlab建模要達到60 dB阻帶抑制比,需要5級級聯。此時,阻帶衰減為單級衰減(13.36 dB)的5倍。由CIC濾波器的傳遞函數,使用Verilog語言即可寫出一個5級、抽取率為2的CIC抽取濾波器和CIC插值濾波器,都由5級積分器和梳狀器級聯構成。但在用FPGA實現的過程中,Integrator模塊里,會出現溢出問題。在設計過程中為防止數據溢出,必須相應地擴大數據的位數,以減少誤差。有相應公式,內部運算單元寬度

REG_WIDTH=L+Nlog2(DM) (2)

其中,L為數據寬度;D為抽取因子;M為差分延遲。

半帶濾波器的本質是FIR濾波器,只是有1/2的系數為0,其實現結果與傳統的FIR濾波器基本相同,將為零的系數通過延遲單元實現,同等條件下復雜度更低。因此,在實現時也可通過FIR Compiler IP核來實現。根據Matlab建模的結果,生成定點量化的半帶濾波器系數,并寫入磁盤,生成coe文件,然后再加載到FIR Complier配置界面中。

在ISE13.1中FIR濾波器的IPCore是FIR Complier,其功能強大,對于半帶的抽取、內插、希爾伯特變換等都能完成,其結構包含乘加結構和分布結構。

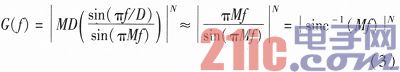

補償濾波器是針對CIC濾波器而設計的,因為CIC濾波器并不具備一個平的、寬的通帶,而多級CIC濾波器會加劇通帶的這種不平坦,所以為了修正通帶內的衰減,可以通過級聯一個FIR濾波器對其幅度響應進行補償。這個FIR濾波器的幅度響應取CIC幅度響應的倒數時,正好可以修正多級CIC濾波器的通帶上的迅速衰降,在擴展其通帶帶寬的同時提高了阻帶衰減。則補償FIR濾波器的幅值響應公式為

由此產生FIR濾波器系數,并由FIR Complier生成。

2 系統的集成與驗證

2.1 下變頻

系統中的各個模塊包括數控振蕩器模塊、5級級聯的CIC抽取與內插濾波器模塊、半帶抽取與內插濾波器模塊和FIR補償濾波器模塊。最后通過編寫頂層文件,實現各個模塊的互聯,以最終集成導航抗干擾接收系統中DUC和DDC的功能。

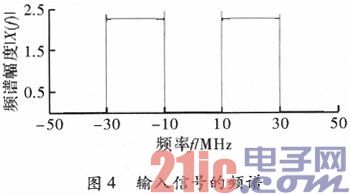

首先在Matlab中產生一個帶寬為20 MHz;中心頻率為70 MHz;頻譜為矩形的信號,以fs=90 MHz的頻率采樣,則其頻譜將在f軸上以fs為周期延拓,原本在70 MHz的頻率上產生的帶寬為20 MHz的中頻信號則會向左以fs的頻率進行周期延拓,并在最靠近零頻的負頻率軸上產生中心頻率為-20 MHz的一個副本。同時由于信號為實信號,將產生-20 MHz與20 MHz上的兩個副本,信號的頻譜如圖4所示。

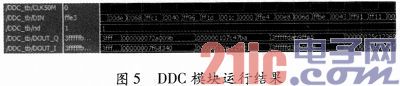

產生16 384個采樣點,將這些數值歸一化并轉換為4位16進制數值,導入DDC的Testbech中,可驗證DDC模塊的功能與正確性。如圖5所示為Modelsim中的仿真結果,DIN為輸入信號,DOUT_Q與DOUT_I為DDC模塊的輸出信號,分別為正交分量和同相分量,其輸出速率降低了75%。

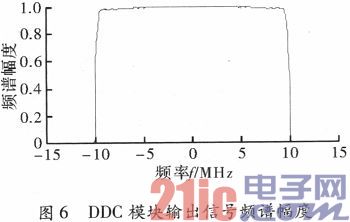

將4 096個同相分量數據和4 096個正交分量數據導入Matlab中進行頻譜分析。可觀察到輸入頻譜為矩形的信號,經過DDC后其波形和頻譜如圖6所示。將輸入波形與頻譜對比,可以看到,其通帶平坦度與阻帶衰減良好,符合預期。

2.2 上變頻

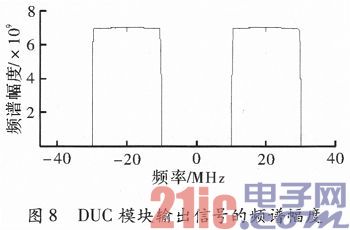

將DDC的輸出信號輸入DUC模塊中,可對數字上變頻模塊進行驗證,信號速率為22.5 MHz,帶寬20 MHz,頻譜如圖6所示。

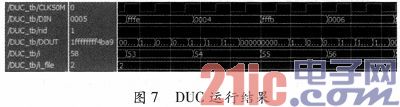

將DDC輸出的4 096個數據歸一化并轉換為4位16進制數值,導入DUC的Testbech中。圖7為DUC模塊對采樣率為22.5 MHz,帶寬20 MHz的基帶信號進行數字上變頻的結果。

將16 384個數據導入Matlab中進行頻譜分析。可觀察到輸入頻譜為矩形信號,經過DUC后其波形和頻譜如圖8所示。

上變頻后數據速率上升到90 MHz,以70 MHz的采樣率進行采樣,經過周期延拓后,中心頻率在20 MHz上。將輸入波形與頻譜對比,數字上變頻設計的結果符合設計期望。

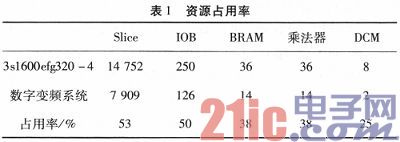

在資源使用上,芯片Spantan3s1600e可以滿足資源需求。其資源占用率如表1所示。

可以看到,Slice的數據在50%~70%之間。此時,可以最大限度地發揮芯片的性能,也為以后的平臺拓展留下空間。從上述數據可以看出,Xilinx芯片的資源利用率是可行的。

2 結束語

設計和實現了導航抗干擾接收系統中的上下變頻模塊。介紹了FPGA芯片的選擇以及集成開發環境。并依據導航抗干擾接收系統的各種參數,對濾波器組仿真并建模,對DUC DDC中每個模塊的FPGA進行設計及功能仿真,通過對整個系統的集成驗證,證明結果符合設計要求,基于FPGA的數字變頻系統應用范圍廣泛、通用性高、修改參數方便、資源使用率較少,可用于通信、信號處理等相關領域移植。

評論