DSP和JTAG接口的FPGA系統在線編程方法

引言

本文引用地址:http://www.104case.com/article/201610/308379.htmDSP+FPGA廣泛地應用于各種數字信息處理系統中。在某些特殊的應用場合中,往往需要系統在高溫的環境下工作,而系統功耗又不明顯增加。雖然一般基于SRAM工藝的FPGA的顯現配置方法已經多種多樣,但使用的基于SRAM工藝的FPGA高溫性能較差,難以滿足高溫、低功耗系統的需要。Actel公司基于Flash工藝的FPGA是為軍工以及宇航設計的器件,完全能夠勝任高溫的需要。一般的FPGA都具有上電功耗、配置功耗、靜態功耗和動態功耗4種,而Actel基于Flash的FPGA由于上電不需要一個很大的啟動電流,并且掉電非易失,不需要配置過程,所以只有靜態功耗和動態功耗,沒有上電功耗和配置功耗。FPGA在高溫下具有更低功耗的優勢。

本文根據Actel公司的產品手冊及相關文件,設計了一種由DSP控制實現FPGA在線編程的方案,使Actel的FPGA能應用于需要在線升級的應用場合中,充分發揮其高溫高可靠性、低功耗的優勢。當FPGA需要在線編程時,只需通過PC下傳FPGA配置命令給DSP,DSP即可把PC下傳的FPGA的配置數據通過JTAG寫入FPGA完成在線升級。該方法的優點在于:無需額外配置芯片(DSP在不需要給FPGA進行在線升級時,可進行其他工作),簡單可靠,在低功耗和高溫的應用中顯得更為重要。

1 方案設計

圖1所示為整體結構設計方案,由PC、UART接口、DSP、RAM存儲器、FPGA以及相應的外圍輔助電路構成。其中TMS320F28335芯片是TI公司2000系列的DSP芯片,A3P250為Actel公司ProASIC3系列的FPGA芯片,RAM芯片為IS61LV51216。DSP的4個GPIO與FPGA的JTAG接口相連,而DSP通過串口轉USB與PC通信。這些芯片都能在125℃環境下正常穩定地工作。其中A3P250一般的靜態待機電流僅幾mA。

系統基本實現步驟為:

①基于VC編寫文件轉換軟件,實現FPGA的程序代碼(.dat文件)轉換成2位十六進制的數據,并存儲在txt文檔中。

②PC發送下載代碼指令至DSP,通知DSP有代碼需要下傳。之后就可以把FPGA程序代碼(txt文檔)以十六進制數據發送給DSP,DSP將收到2位十六進制數據存至外部RAM中。每個地址存兩個2位十六進制數據,先存低位,再存高位(存入RAM是由于FPGA的程序代碼量比較大)。

③DSP對下載的代碼進行CRC校驗,回傳調試信息。若代碼CRC校驗成功,PC就可以發送編程指令通知DSP給FPGA編程。

④DSP控制FPGA JTAG實現讀取FPGA設備的ID,驗證是否與配置數據中的ID一致。成功,則開始FPGA編程。DSP實時回傳編程的調試信息給PC,方便觀察調試。編程成功之后,FPGA即可正常運行。

由于串口傳輸過程只需要兩根信號線,即傳輸線TX以及接收線RX,故傳輸協議簡單,且較好地避免了JTAG距離的限制。同時,系統在需要對DSP的配置控制功能進行升級時,也可以通過串口實現。

2 方案實現

2.1 系統硬件設計和實現

根據方案設計,配置控制電路如圖2所示。在本系統中FPGA的JTAG口與DSP的GPIO相連,DSP的SCIA接口經RS485收發器和串口轉USB芯片連接至PC,實現指令下傳至DSP和調試信息上傳至PC。DSP在外部接口(XINTF)的ZONE7區(共3個區域,另兩個為ZONE0、ZONE6)外部擴展1片512 KB×16的外部RAM,用以存儲FPGA的配置碼流。F28335的XINTF區域可以通過編程來配置特定的等待狀態數,選通信號的建立和保持時間,而且讀寫訪問可以獨立配置。當片選信號被拉低時,用戶可以訪問該區域。如當程序訪問0x00300000時,就會產生外部地址0x00000和ZONE7區片選信號(

)。另外,需特別注意的是,在編程電壓VPUMP和地之間需接0.01μF和0.33%20%20μF濾波電容。不接,可能會導致JTAG邊界掃描接入失敗等問題。通過PC下傳下載代碼指令,DSP接收FPGA的配置碼流并保存在外部RAM,之后PC就可以下傳指令,命令DSP給FPGA再編程。

2.2 系統軟件設計和實現

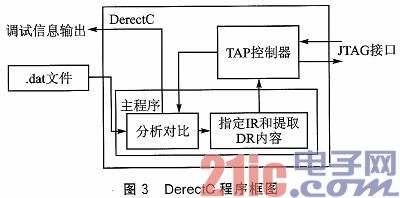

2.2.1 DerectC介紹和移植

Actel公司基于Flash的FPGA只能通過JTAG接口,而JTAG使用的距離較近,程序升級必須拆卸系統封裝,較為麻煩,且容易造成零部件損壞。Derectc3.0是Actel提供的一系列C源程序代碼,通過移植它到不同的微處理器,將微處理器通用I/O(需支持LVTTL電平)連接至FPGA的JTAG接口,實現FPGA的擦除或再編程。DerectC不包含任何與應用或者設備相關的信息,它只負責解析配置文件中的內容,在JTAG接口上產生用于配置的二進制數據流并讀取反饋數據,適用于IGL002、SmartFusion2、ProASIC3、IGLOO、Smart Fusion和Fusion系列。DerectC程序框圖如圖3所示,DerectC需使用Libero生成的.dat格式的FPGA配置文件,文件需要LiberoV8.5以上才能獲得。在Libero SoC v11.1中,只需點擊gene rate programming data選項即可獲得。在使用DerectC時,只需對它作一些修改,增加一些必要的API函數,然后添加至C工程中即可。

把DerectC移植到DSP中,主要經過以下步驟:

①針對使用的FPGA系列,添加和去除預處理語句,去除不必要的代碼;

②將JTAG信號映射到具體的DSP硬件引腳;

③添加JTAG輸入輸出函數和配置文件數據塊讀取函數等必要的API函數。

對于IGLOO2、SmartFusion2、IGLOO、Smart Fusion和Fusion系列的FPGA,移植過程是完全一樣的。移植完成后,對于以上提到的所有Actel的FPGA芯片都可以實現在線編程,只是FPGA的配置電路中濾波電容的個數可能稍有差異。

另外,DerectC還支持FPGA的菊花鏈編程。在移植DerectC時,只需設置好在邊界掃描鏈中IR和DR的長度和額外支持菊花鏈的預編譯指令。此時只需一塊DSP就可以依次完成多塊FPGA的在線升級,大大節省了硬件開支。

2.2.2 配置文件格式及轉換

A3P系列Libero產生的配置文件包含3個方面的內容:

①頭塊:包含二進制文件的識別信息(軟件版本號等)、數據塊的數目、總的字節長度、目標設備ID和DerectC識別所支持的塊所需的標志位等,共69字節。

②數據查找表:在DerectC中使用到的各數據塊在文件的相對起始地址以及長度,每個數據占5字節。

③數據塊:二進制數據碼流,用于給FPGA在線編程的主要數據,總長度以字節為單位,最后包含總的data文件的CRC校驗碼。

方便下傳數據,基于VC把整個二進制data文件轉換成2位十六進制的數據流并存儲在TXT文檔中,同時在文件的頭部加入表明整個data文件長度的4字節,以方便PC指示DSP下傳的數據長度。具體為VC以二進制的形式打開配置文件,讀取其長度寫入TXT文檔,并每次讀取8位二進制數據轉換為2位十六進制數據。DSP把收到的數據依次存在DSP的外部RAM(每個地址存兩個字節),先存低位,再存高位。

2.2.3 配置程序數據的下載實現

本設計PC通過USB轉串口向DSP發送指令,以指示DSP需要進行什么樣的操作。表1為常用的幾個串口指令,指令長度都為2字節。

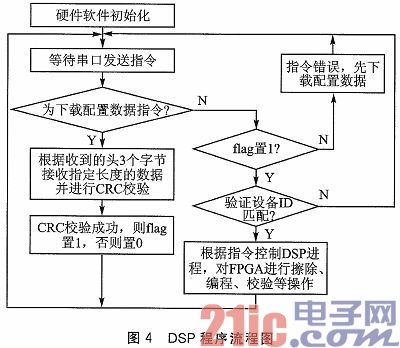

DSP的主程序流程圖如圖4所示。DSP串口中斷等待PC下傳FPGA在線編程指令,對收到的FPGA配置數據流進行CRC校驗,保證程序的完整性。之后DSP接入FPGA邊界掃描鏈,在JTAG每個TCK上升沿讀取TDI的數據或向TD0輸出1位數據,在DSP把IR操作數內容寫入IR,FPGA會自動把DR放入邊界掃描鏈,進行FPGA的數據讀出與寫入,從而實現讀取FPGA設備ID與配置數據流中的設備ID匹配、FPGA的擦除、配置文件中的數據塊寫入FPGA等操作,完成在線升級。

3 試驗結果分析

為了確保配置控制方法的可靠性,通過串口往DSP下傳經過VC轉換的FPGA配置文件,DSP接收到全部配置文件后會進行CRC校驗。檢驗的結果通過串口實時回傳至PC,保證了配置文件的完整性。之后DSP讀取FPGA的設備ID,與配置文件的ID進行對比,確保目標設備的正確性,結果同樣通過PC顯示出來。

在上述驗證通過的情況下,DSP開始對FPGA進行擦除操作,之后向FPGA中燒寫跑馬燈配置碼流數據。和Actel的FlashPRO3編程器一樣,燒寫完成之后會對編程結果進行驗證,確保燒寫的正確性。以上過程中,DSP串口會返回調試過程信息給PC,以表明程序燒寫進程。整個過程完成后,LED燈按預期程序設計有規律地閃爍,無需重新啟動。在實驗系統環境中,一次配置的時間約為97 s,與使用Actel的FlashPRO3編程器的時間相差無幾,配置時間很短。

結語

本設計實現了一種基于DSP GPIO口驅動FPGA的JTAG接口,以及串口對Actel FPGA進行系統的在線編程。不僅適用于某一型號的Actel的FPGA,而且適用于IGLOO2、Smart Fus ion2、ProASIC3、IGLOO、Smart Fusion和Fusion系列,適用范圍很廣。另外,該設計簡單,只需將DSP的GPIO與FPGA的JTAG中4個必要的引腳相連,串口下傳指令和FPGA配置數據,無需額外的配置芯片,避免了JTAG距離的限制,且采用的芯片完全滿足高溫、低功耗的要求,具有高速高、可靠性等優點,方便多任務的切換。使用本系統無需重啟就可以動態地更新FPGA應用,使得Actel的FPGA應用能不受在線升級的距離困擾。

評論