基于ARM處理器S3C2440A的便攜式視頻展示臺的設計

3.3 VGA驅動設計方案

3.3.1 LCD幀緩沖設備驅動結構

幀緩沖是Linux為顯示設備提供的一個接口,它把一些顯示設備描述成一個緩沖區,允許應用程序通過FrameBuffer定義好的接口訪問這些圖形設備,而不用去關心具體的硬件細節。對于幀緩沖設備而言,只要在顯示緩沖區與顯示點對應的區域寫入顏色值,對應的顏色就會自動的在屏幕上顯示。LCD控制器驅動是VGA設備驅動的核心,是一個標準的linux2.6內核下的framebuffer設備驅動。在VGA驅動設計的過程中首要的是配置LCD控制器。而在配置LCD控制器中最重要的一步則是幀緩沖區(FrameBuffer)的指定。因此,驅動幀緩沖是實現是整個驅動開發過程的重點。幀緩沖驅動需要完成的的工作主要有5個部分:編寫初始化函數,編寫成員函數,讀寫,映射,輸入輸出控制。

1)初始化LCD控制器

通過寫寄存器,設置顯示模式和顏色數,然后分配LCD顯示緩沖區。緩沖區大小為:點陣行數×點陣列數×用于表示一個像素的比特數/8。緩沖區通常分配在大容量的片外SDRAM中,起始地址保存在LCD控制寄存器中。文中采用的LCD顯示方式為800x600,需要分配的顯示緩沖區為960 KB。最后是初始化一個fb_info結構,填充其中的成員變量,并調用register_framebuffer(tb_info),將fb_info登記入內核。

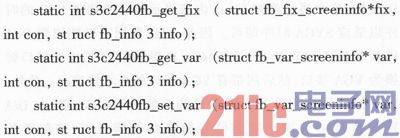

2)編寫成員函數

該函數主要用于編寫fb_info()結構體中指針fb_ops()對應的底層操作函數,主要是3個函數:

以上這些函數都是用來獲取fb_info()中的成員變量的,當應用程序調用ioctl()操作時將會調用這些函數。

讀寫函數就是用來讀寫屏幕緩沖區,地址映射操作可以將文件的內容映射到用戶空間,這樣用戶就可以通過讀寫這段地址來訪問緩沖區了。輸入輸出操作就是設備文件ioctl()讀取和設置顯示設備的參數,具體的ioctl()的實現由底層驅動程序來完成。

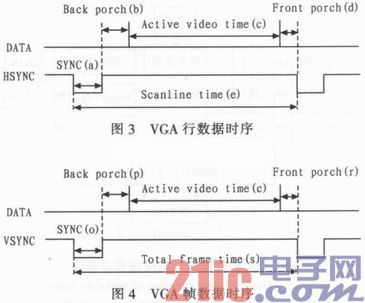

3.3.2 根據VGA時序設定LCD控制器寄存器

本便攜式視頻展示臺選擇SVGA顯示,像素時鐘信號VCLK為40 MHz,分辨率為800x600,幀頻率為60 Hz,16位真色彩顯示,SVGA時序如下圖所示。本文引用地址:http://www.104case.com/article/201610/306063.htm

根據圖3、圖4所示SVGA顯示時序的特點,對LCD控制器中的控制寄存器進行如下配置。

1)LCDCON1寄存

CLKVAL:確定VCLK頻率的參數。公式為VCLK=HCLK/[(CLKVAL+1)x2],在本設計中S3C2440A的HCLK=100MHz,VCLK=40 MHz,故需設置CLKVAL=0.25,設置BPPMODE=0xC,即選擇TFT 16位模式。

2)LCDCON2寄存器

VBPD:確定幀同步信號和幀數據傳輸前的時延,是幀數據傳輸前延遲時間和行同步時鐘間隔寬度的比值,如圖4所示,VBPD=p/c=0.6 ms/20 μs=30。

VFPD:確定幀數據傳輸完成后到下一幀同步信號到來的一段延時,是幀數據傳輸后延遲時間和行同步時鐘間隔寬度的比值,VFPD=r/c= 0.026 ms/20μs=10。

LINEVAL:確定顯示的垂直方向大小,LINEVAL=YSIZE-1=599。

VSPW:確定幀同步時鐘脈沖寬度,是幀同步信號時鐘寬度和行同步時鐘間隔寬度的比值,VSPW=o/c=0.1 ms/20μs=5。

3)LCDCON3寄存器

HBPD:確定行同步信號和行數據傳輸前的延時,描述行數據傳輸前延遲時間內VCLK脈沖個數,HBPD=bxVCLK=2.2μsx40 MHz=88。

HOZAL:確定顯示的水平方向尺寸。這里HOZAL=XSIZE-1=799。

HFPD:確定行數據傳輸完成后到下一行同步信號到來的一段延遲時間,描述行數據傳輸后延遲時間內VCLK脈沖個數,HFPD=dxVCLK=1 μsx40 MHz=40。

4)LCDCON4寄存器

HSPW:確定行同步時鐘脈沖寬度。描述行同步脈沖寬度時間內VCLK脈沖個數,HSPW=axVCLK=3.2μsx40 MHz=128。

5)LCDCON5寄存器

BPP24BL:確定數據存儲格式。此處設置BPP24BL=0x0,即選擇小端模式存放。

FRM565:確定16位數據輸出格式。設置FRM565=0x1,即選擇5:6:5的輸出格式。

4 結束語

文中根據市場對視頻展示臺的大量需求現狀,提出了基于ARM9的S3C2440的便攜式視頻展示臺的設計方案。與用CPLD/FPGA來實現VGA顯示的系統相比,本方案節約成本和資源,且接口電路簡單,應用靈活、可靠。由本方案做成的視頻展示臺體積小,易于攜帶。本方案經過Linux軟件測試論證,方案切實可行,對實物、圖片、文檔或者過程的顯示效果清晰,無抖動。

評論