多方位多角度 帶您重新詮釋多核技術

UltraSPARC T1的 CoolThreads技術也具有類似的動態轉移功能,任何一個執行單元有空余時,都可抓取已排入其他位置的待處理線程加以執行,由此維持八個核心的均衡負載。

UltraSPARC T1的整合內存控制器相當強大,它并不是像常規多核處理器一樣只內建1組,而是擁有多達4組內存控制器,每個控制器都可以支持雙通道ECC DDR2-533MHz內存、傳輸位寬達到144bit。在運行過程中,如果有4bit以下的內容錯誤,UltraSPARC T1的內存控制系統可自行糾正,如果錯誤數量提高到8bit,UltraSPARC T1仍然具備識別能力,系統可保持長時間的穩定運作。

另外,每組內存控制器都可以連接4個DIMM內存槽,因此一枚UltraSPARC T1處理器最多可管理多達16個DIMM模組,創造該領域的最高記錄。毋庸置疑,UltraSPARC T1以4組144bit內存接口來對應8核心已經是相當充足,但SUN提供了更多的選擇。在必要時候,用戶可以將每兩個控制器捆綁在一起,相當于將原本相互獨立的4組內存系統變成兩組可并行存取的結構,從而將內存系統的傳輸速度提高一倍。倘若系統執行的任務對數據傳輸有很高的要求,開啟這項功能將對系統性能提升起到立竿見影的作用。

而在多路擴展方面,UltraSPARC T1采用的是SUN獨有的JBus高速互聯總線,JBus 1.0規格早在2003年4月就發布,采用128bit位寬的地址/數據接口,總線頻率在150MHz-200MHz之間,峰值傳輸速率可達到 3.1GBps。雖然成就遠不如AMD的HyperTranspot總線,但JBus的性能同樣可滿足多處理器數據交換的要求,畢竟UltraSPARC T1擁有八個核心和32個獨立線程,處理器之間不需要交換太多的數據。

除了八核心版本外,SUN公司還將推出較低定位的六核心、四核心UltraSPARC T1,但三者其實都出自相同的晶圓,只是將存在瑕疵、但關閉部分內核后可正常運行的芯片作為六核或四核型號。令人驚訝的是,UltraSPARC T1非常節能,在八核心、32個線程都激活狀態下的典型功耗僅有72瓦,峰值功耗也只有80瓦,能源利用效率極其出色;另外,UltraSPARC T1還可以通過關閉某些核心來達到節能的目的。

當然,我們不能簡單將UltraSPARC T1與X86處理器作直接的對比,畢竟兩者面向不同的應用、設計思想迥異。但從UltraSPARC T1中我們可以接觸到另外一種設計思想:即根據特定的應用來設計處理器,使得該處理器能夠在既定應用中獲得最佳的效能。這種思想在RISC業界已經開始風行,X86處理器受通用所累,暫時難以實現類似設計,但在未來我們不排除這種思想被X86業界借鑒的可能:例如英特爾/AMD可以專門針對游戲玩家和多媒體娛樂用戶設計出強化浮點性能的娛樂型處理器,或者設計出強化整數性能、功耗更低的辦公型處理器,這樣辦公用戶不必為自己不需要的浮點性能多掏腰包,娛樂用戶也能夠獲得性能更出色的產品。而對英特爾、AMD廠商來說,只要設計一個富有彈性的處理器架構,制造出不同定位的產品并不需要花費多少代價。

專用協處理器實現效能跨越

PWRficient的高度整合思想、SUN UltraSPARC T1根據任務定制的精簡核心、多任務方案令人耳目一新,但這兩者其實都只是在現有多核架構基礎上的革新,處理器本身仍然基于對等的多核心設計。

微處理器領域真正意義的架構革命將在未來數年內誕生,那就是多核架構將從通用的對等設計遷移到“主核心+協處理器”的非對等設計,亦即處理器中只有一個或數個通用核心承擔任務指派功能,諸如浮點運算、HDTV視頻解碼、Java語言執行等任務都可以由專門的DSP硬件核心來完成,由此實現處理器執行效率和最終性能的大幅度躍進—IBM Cell、英特爾Many Core和AMD HyperTransport協處理器平臺便是該種思想的典型代表。

下面,我們便從Cell入手,向大家介紹這種極具前途的新穎設計。

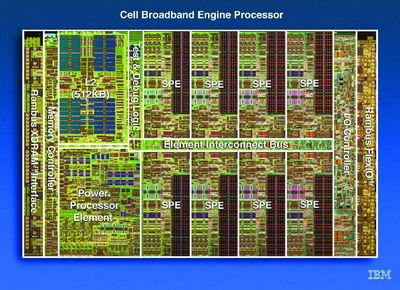

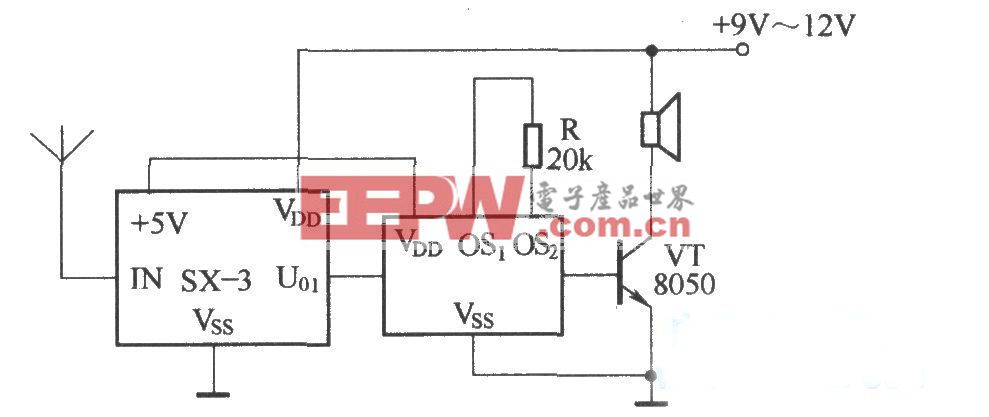

圖3 Cell處理器基于“PPE主處理單元+SPE協處理器”的專用化設計,實現浮點性能的飛躍。

IBM Cell:開創全新的多核架構

IBM為索尼PS3游戲機定制的Cell是一枚擁有9個硬件核心的多核處理器,它的多核結構同以往的多核心產品完全不同。在Cell芯片中,只有一個核心擁有完整的功能,被稱為主處理器,其余8個核心都是專門用于浮點運算的協處理器。其中,主處理器只是PowerPC 970的精簡版本,其主要職能就是負責任務的分配,實際的浮點運算工作都是由協處理器來完成。

由于Cell中的協處理器只負責浮點運算任務,所需的運算規則非常簡單,對應的電路邏輯同樣如此,只要CPU運行頻率足夠高,Cell就能夠獲得驚人的浮點效能。而由于電路邏輯簡單,主處理器和協處理器都可以輕松工作在很高的頻率上—Cell起步頻率即達到4GHz就是最好的證明。在高效率的專用核心和高頻率的幫助下,Cell獲得了高達256Gigaflops(2560億次浮點運算每秒)的浮點運算能力,接近超級計算機的水準,遠遠超越目前所有的X86和RISC處理器。

作為對比,英特爾的4路Montecito安騰(雙內核)系統也僅獲得45Gigaflops的浮點性能。更令人驚訝的是,Cell只花費了區區2.34億個晶體管,功耗在80-100瓦左右,能源利用效率比現在設計最佳的RISC和X86處理器都高出數十倍,這足以說明Cell專用、多核設計思想的優越性。

必須提到的是,Cell并非通用的處理器,雖然它具有極強悍的浮點運算性能,可很好滿足游戲機和多媒體應用,但整數性能和動態指令執行性能并不理想,這是由任務的形態所決定的。未來耗費計算機運算性能最多的主要是3D圖形、HDTV解碼、科學運算之類的應用,所涉及到的其實都是浮點運算,整數運算只是決定操作系統和應用軟件的運行效能(操作系統、Office軟件等),而這部分應用對處理器性能要求并不苛刻,因此Cell將側重點放在浮點運算性能,與SUN UltraSPARC T1專注事務處理的設計可以說有異曲同工之妙。

相較而言,當前的X86處理器都采用通用的核心,為了同時提高整數性能和浮點性能,CPU核心被設計得越來越臃腫,晶體管消耗越來越多,不僅導致芯片的功耗急劇增大,頻率提升速度也非常緩慢。而且通用設計的另一個弊病在于,不管執行什么任務,芯片內的所有邏輯單元都消耗電力,導致X86芯片普遍存在能源利用率低的問題。

評論