基站調制解調器――為什么要現在選擇多核?

根據功能分配任務

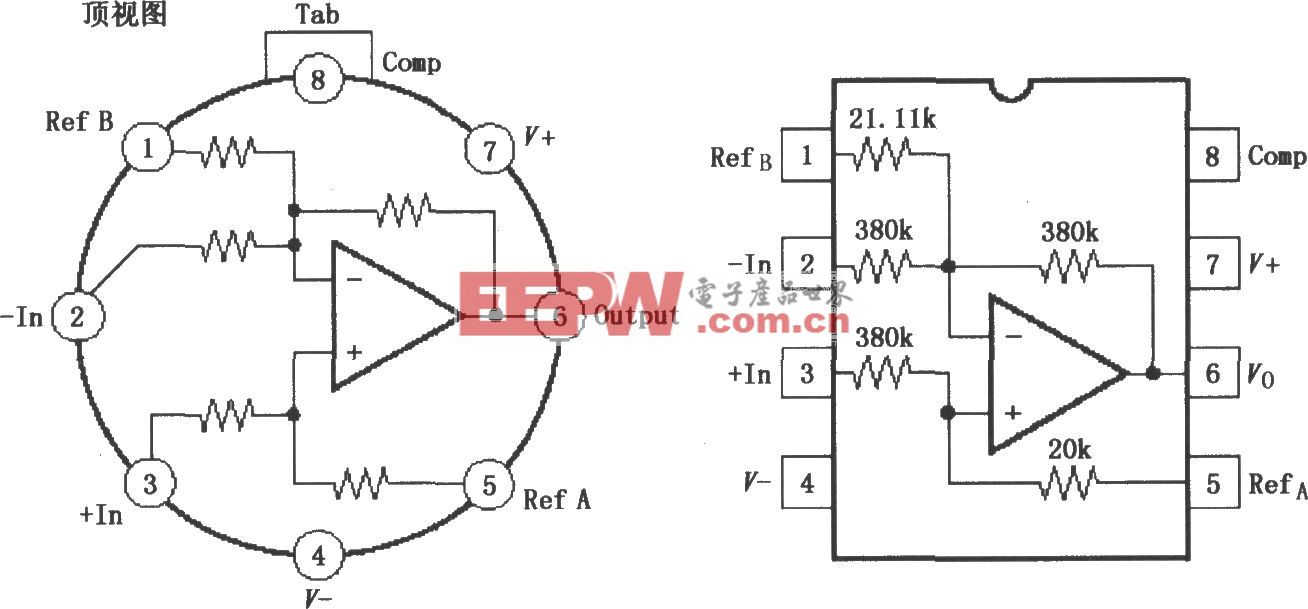

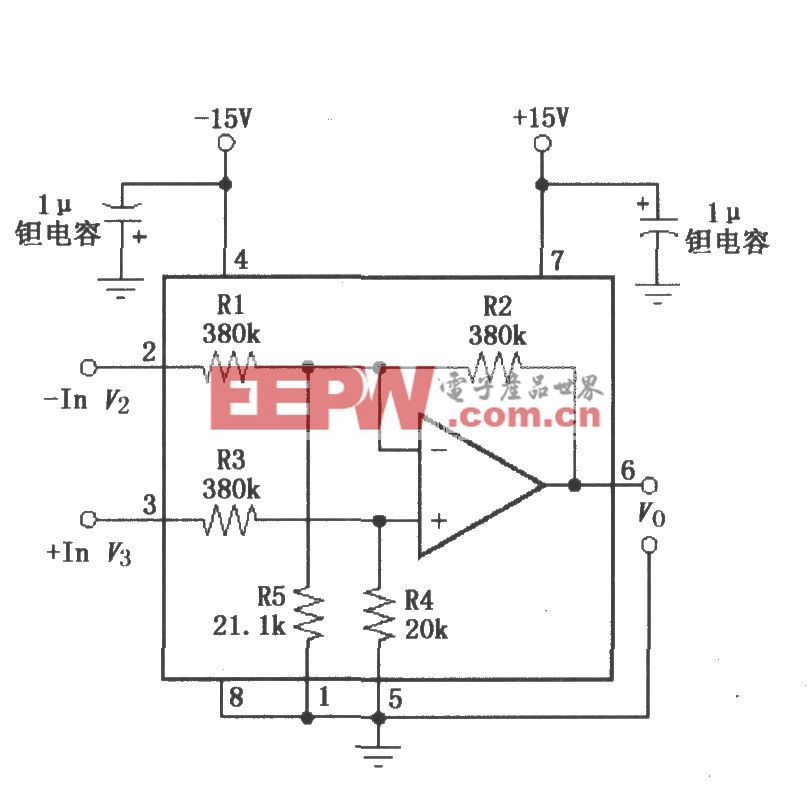

圖 3 所示系統(tǒng)存在 7 項針對2 名用戶按顏色劃分的任務,其按功能分配。

圖3:根據功能進行的任務分配。

在這種設計中,內核無需知道系統(tǒng)中存在多少用戶。相反,它只需知道必須執(zhí)行多少個唯一功能。隨著用戶數量增加,完成一項任務的時間也會隨之增加。

如果在數據可用時立即調用某項任務,則會為每個用戶調用每項任務,而且任務切換次數隨用戶數量增加而增加,這種情況會造成大量的任務切換次數。更好的方法是為每項任務分配一個鏈接列表。當任務完成時,將在該用戶中執(zhí)行作為該任務(與下項功能相關聯)鏈接列表項目的系統(tǒng)。

這種方法不會隨著用戶在鏈接列表中的累加而產生中斷。在每項任務被激活時,它會完成其鏈接列表或者運行至鏈接列表被搶占為止。其中一種選擇是僅允許鏈接列表用戶處理之間的搶占,這樣用戶功能就永遠不會中斷。這種選擇可以在存儲需求最低狀態(tài)下實現搶占,因為所有需要的狀態(tài)已經保存到相關列表中了。

其中一個關鍵的考慮事項是激活任務的頻率:

• 簡單的周期性中斷:通過將任務分組到少量優(yōu)先級隊列可以進一步簡化此類中斷。在 WCDMA 中,只需兩個隊列即可獲得良好的性能。其中存在單個周期中斷,內核在切換到低優(yōu)先級隊列之前先清空高優(yōu)先級隊列。高優(yōu)先級任務允許搶占時間更長的低優(yōu)先級任務,而不需要隨用戶數增加的數據驅動中斷。需要計算中斷周期,以確保能夠在最后期限之前以足夠快的速度完成高優(yōu)先級任務的最差情況負載。

• 多個周期中斷:其能夠迅速完成高優(yōu)先級隊列,同時在完成較低優(yōu)先級隊列之前保留盡可能多的時間。因此,只要不全部完成高優(yōu)先級隊列,就不會遺留低優(yōu)先級隊列中的任務。

• 隊列達到特定大小時的中斷:這是希望將中斷次數最小化時執(zhí)行隊列的最有效方式,但是它會使任務的延遲取決于到達任務的數量。因此它不太適用于嚴格的實時系統(tǒng)。

• 隊列頭 (head of queue) 達到特定時限時的中斷:可以實現一定時間內一定水平的服務保證,同時將中斷次數最小化。為了實現上述目的可以為每個隊列 頭設置一個定時器,然后在定時器達到指定值時產生中斷。如果需要處理隊列頭,則必須采取某種方法將定時器重新設置到下一個隊列項目的等待時間長度。其適用于需要跟蹤隊列中各項任務所耗時間的復雜系統(tǒng)。

為了將任務數量和任務搶占開銷保持在可控水平,它們不可根據用戶數量而定。相反,任務應當與功能而不是與用戶關聯。由于目前的 BTS 為了實時滿足客戶需求而必須承擔更多數據流量,因此這種設計越來越重要。

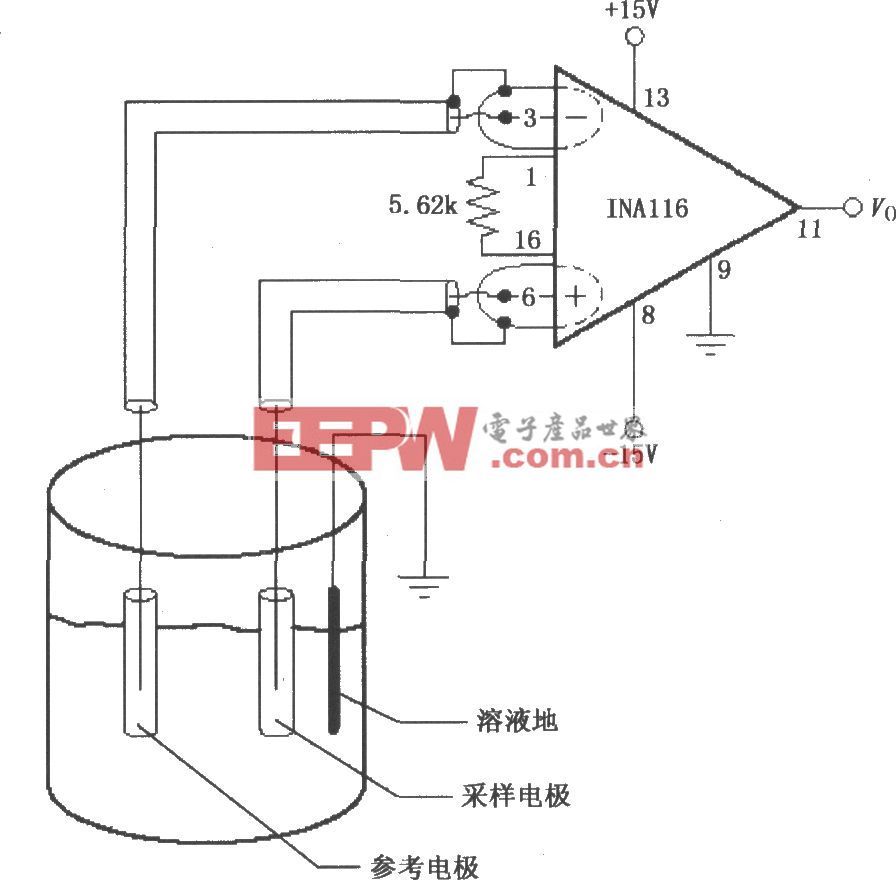

多核考慮

當今的 SoC 一般是多核 CPU ,采用獨立的 IP 塊,為了實現一個完整的調制解調器功能必須實現互操作和同步化。這種架構需要某種方式將優(yōu)先級隊列系統(tǒng)(圖 4)映射至多 CPU 環(huán)境。

圖4:基于功能的任務優(yōu)先級隊列。紅色箭頭表示處理順序的依存性。

最簡單的選項是將用戶分配到相關 CPU,使每個 CPU 都保持其自己的隊列。但是這樣會有兩個缺點:第一,所有用戶有可能共享某些功能(如過濾與解調)。第二,某些功能可能需要共享協(xié)處理器或外設,造成它們不具有完全獨立性。這樣會造成一系列優(yōu)先級隊列之間的交互復雜化,從而難以保證實時性能。由于必須要支持多個 CPU 的存取,協(xié)處理器和外設也將變得更為復雜,因此必須決定 CPU 的哪項任務優(yōu)先。所有這些都會增加軟、硬件驅動程序的復雜性,使最終系統(tǒng)的測試更加困難、更加耗時。

為避免這些缺點,TI 采取了不同的方案:為單個 CPU 分配功能任務,從而使每個 CPU 都負責唯一一組功能。一般只加速特定類型功能的每一個協(xié)處理器都與單個 CPU 關聯。這種方法可以顯著簡化協(xié)處理器所執(zhí)行任務的排序。在許多情況下,外設也會與單個 CPU 通信,從而減少對不缺乏數據的任務進行檢驗所需的測試。

TI 的設計采用全系統(tǒng)同步排列 CPU 的幀、時隙 (slot) 與符號邊界。這種通信采用由一項任務產生、發(fā)送到另一個任務的數據塊來實現,一般由 L2 存儲器之間的 DMA 執(zhí)行。(每個 CPU 都具有其自己的 L2 存儲器,因為共享存儲器需要在速度等方面做出權衡折中。)

由于 TI DSP 可用于眾多功能,因此 TCI6488 SoC具有高度的對稱性。例如,所有 CPU 都可以訪問接收機加速協(xié)處理器 (RAC)。這種設計允許在所有 CPU 上運行相同的功能并且允許所有 CPU 訪問所有協(xié)處理器和外設資源。不過,TI 建議系統(tǒng)設計人員讓一個 CPU 與 RAC 交互,以簡化器件的操作。

通過實現 CPU的資源負載平衡,根據每項任務所采用的代碼,一個 CPU 可能會先于其他 CPU 達到最高容量。解決方案是進行重新分組,但這需要軟件架構改頭換面 —— 這是在完成 CPU 測試時設計人員更愿意避免的情況。TI 相信,軟件無線電方法與工具的進步會讓軟件分配變得更為輕松。

TI 采用代碼周期估算、電子表格以及事務處理級模型來開發(fā)用于 WCDMA TCI6488 SoC 的建議軟件分組。TI 相信,這種分組可以提供近乎完美的解決方案,同時仍然保留以下簡單性:用一個 CPU 控制 RAC、一個 CPU 控制 TCP 和 VCP,以及用一個 CPU 執(zhí)行 Tx 芯片頻率加速和與天線陣列接口的輸出通信。

對于其他標準(如不采用 RAC而是基于 OFDM 的標準),更易于開發(fā)對稱軟件架構。不過,即使在這些情況下仍然更便于分配此問題,這可以讓一個 CPU 執(zhí)行 FFT/IFFT 和部分調制/解調任務,而將相關結果發(fā)送至另一個 CPU 以便進行符號率處理。若用于天線數據,這種方法可以簡化天線接口 或串行 RapidIO 與負責前端處理的 CPU 之間的通信。另外,其還可以簡化后端符號率處理及其與以太網或串行 RapidIO 的通信。

評論