淺析SoC芯片設計中的動態功率估算挑戰

設計尺寸的增長趨勢勢不可擋,這也一直是EDA驗證工具的一個沉重負擔。動態功率估算工具即是其一。

本文引用地址:http://www.104case.com/article/201609/303679.htm總有一些刺激因素誘使著客戶頻繁升級他們的移動設備。其中包括更多功能和改進的用戶體驗,更具吸引力的用戶界面,更輕的重量、更持久的電池壽命等等,不勝枚舉。從各方面考慮,似乎持久的電池壽命位居榜首,而更長的電池壽命直接關系到更低的功耗。

自從五十年前Noyce和Kilby發明平面集成電路以來,微電子產品的功耗經歷了一段穩定下降期。平面技術使得縮放(縮小)固態器件成為可能。晶體管尺寸越小,同一區域內容納的晶體管數量就越多,切換速度就越快,所消耗的能量就會越少,而芯片運行時的溫度也會越低(相較于相同數量的晶體管而言)。

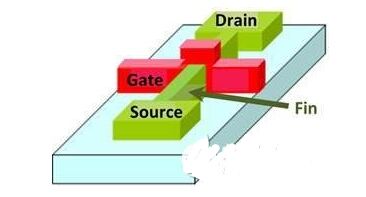

“Doublegate FinFET”,作者:Irene Ringworm,發布在英語維基百科上。通過維基共享資源依據CC BY-SA 3.0協議獲得授權。

在歷史上,微電子產品發展的衡量標準一直著眼于場效應晶體管中源極和漏極之間硅通道的長度(被稱為工藝技術節點)。上世紀60年代初,該節點為50微米。十年后,這一數字下降到了1微米以下,而到了2003年,則達到100納米以下,開啟了納米技術時代。

在前二十年,由于漏電問題,晶體管未切換且空閑時的靜態功耗遠小于晶體管切換狀態下的動態功耗,小到可以忽略不計。到了180納米時,靜態功耗開始飛速上升,到了2005年,由于節點降到了65納米以下,靜態功耗超過了動態功耗。

不必擔心。FinFET或3D晶體管的發明及時地拉住了滑向消失深淵的平面晶體管。

FinFET預計可減少多達90%的靜態泄漏電流,并且僅使用等效平面晶體管50%的動態功率。與平面等效晶體管相比,FinFET晶體管在同等功耗下運行速度更快,或在同等性能下功耗更低。有了FinFET,設計團隊可以更好地平衡產量、性能和功率,滿足各個應用程序的需求。

功率估算挑戰

如前所述,更低的工藝節點帶來了更高的晶體管密度,這使設計團隊有機會在其中加入越來越多的功能。如今,在最大型的設計中,晶體管數量超過了100 億。遺憾的是,設計尺寸的增長趨勢勢不可擋,這也一直都是 EDA驗證工具的一個沉重負擔。動態功率估算工具即是其一。我們可以假定,電路的動態功耗與電路在運行時發生的邏輯轉換次數成比例。因此,要精確地估計和優化數字電路的功率,我們需要記錄每個時鐘周期內每個設計元素的切換活動,并將該活動饋入工具執行功率相關的任務中。

在不跟蹤相應周期的情況下記錄切換活動可獲得運行時段內的平均功耗。通過添加按周期記錄的信息可以跟蹤峰值功耗。

我們直覺上會假設記錄切換活動的準確性會隨著設計說明從高層次抽象下降到門級,進而又下降到晶體管級而增加,原因是可用的設計詳細信息越來越多。

現在的困境是,在電子系統級(ESL),設計人員在對比多個架構、多種場景或軟件算法并實現最佳功率優化方案上擁有了前所未有的靈活性。糟糕的是,在說明級別,功率估算卻不夠準確。在門級,可以獲得的詳細信息極少,靈活性也非常有限,僅可支持完成邊緣優化,在晶體管級更是如此。而在寄存器傳輸級 (RTL),似乎可以實現最佳折中。既可以獲得足夠的詳細信息來實現功率的適當估算,又有足夠的靈活性來實現較大的功率優化。

動態功耗在很大程度上取決于應用于其主要輸入設備的激勵或在嵌入式SoC設計時代由嵌入式處理器執行的嵌入式軟件所觸發的設計內的活動。也就是說,通過啟動操作系統或執行驅動程序、應用程序或診斷。

諸如模擬器和仿真器等驗證引擎是用于跟蹤切換活動的完美工具。要提醒的是,模擬器的執行速度主要取決于設計級別說明、設計大小和應用于設計的激勵類型。為了減輕并消除此類依賴,同時為了處理嵌入式軟件,只有仿真器可以在合理的時間段內執行這一挑戰性任務。

截至目前,估算功耗一直采用兩步法:第一步,模擬器或仿真器會在一個交換格式 (SAIF) 文件中跟蹤并累積整個運行過程中的切換活動,或在快速信號數據庫(FSDB)文件中按周期記錄每個信號的切換活動。第二步,使用一個饋入SAIF文件的功率估算工具計算整個電路的平均功耗,或使用饋入FSDB文件的功率估算工具計算設計時間和空間內的峰值功率。

上述機制對于SoC設計而言有兩個問題。SAIF和FSDB文件巨大且幾乎無法管理,且需要長期維護。在十億門設計時代,這兩個問題結合在一起使上述方法沒有了用武之地。

評論