基于機器視覺的車道偏離預警系統的實現

2、系統設計與實現

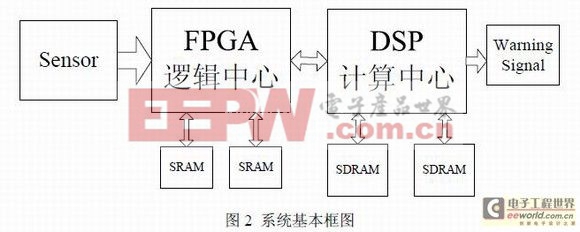

實現圖 2 的基于視覺的汽車主動安全系統,數據的存儲和傳輸是一個主要的問題,尤其是對于汽車主動安全這樣的實時性要求非常高的應用背景。如何在最短的時間內,由原始采集到的圖像數據,經過一系列的存儲器數據搬移及信號處理過程,獲得最終的對道路的理解判斷,并對車輛是否跑偏做出正確的決策,是本系統主要的實現目標。本文將依據數據在系統中的“流動”順序對本系統進行詳細的介紹。

2.1、數據采集模塊

在本系統中,圖像數據是主要的傳感器信號,獲得高質量的圖像數據對后期的處理和功能的實現具有較大的意義。但是對于實際的應用環境,由于天氣、光照等因素的影響,甚至是一系列特殊情況的出現,一般的圖像傳感器在各種條件下難以具有較好的魯棒性。為了較好的適應各種道路和天氣狀況,保證駕駛的安全性,我們采用了適合道路使用的CMOS 數字攝像頭芯片自主開發了視覺采集模塊,該攝像頭芯片通過159 位SPI 控制字可完全編程控制,較好的實現對曝光時間、增益和噪聲等的調節。同時,該攝像頭芯片采用了一種多斜率的曝光模式輸出,在不同的曝光模式下,控制曝光的時間也是不一樣的,保證在光照過強或者光照條件非常弱的情況下,都可獲得較好的圖像。

對于攝像頭芯片的SPI 控制,本文為了自適應的調整在不同背景下的工作模式,由DSP根據最后對圖像的理解和判斷的結果,給予FPGA 一定的通信信號完成對攝像頭芯片的頂層的系統級的控制,而底層的真正的SPI 控制字的修改和調整則由FPGA 來完成,這樣可避免SPI 的工作頻率和DSP 外部總線頻率的不一致而導致的DSP 工作效率的浪費,而FPGA來完成這樣的工作則比較容易。

2.2、數據傳輸、存儲模塊

在本系統中,從前端的圖像采集模塊,到最后的報警信號的輸出,數據是不停的在FPGA、SDRAM 及DSP 之間進行傳輸和搬移,接下來主要討論如何在這三者之間進行高速有效的搬移和處理,這也正是本文的主要模塊。系統中的數據流程主要有以下幾個方面:

Ⅰ、在 FPGA 中經過預處理的圖像數據,首先必須存儲到主存儲芯片SDRAM 中,這是后端高層處理的基礎。

Ⅱ、DSP從SDRAM中讀取最新的圖像數據進行處理,并將處理的中間結果存于SDRAM中,這樣的讀寫過程很可能是循環進行的,SDRAM 的分塊存儲特性正適合這樣的性能要求。

Ⅲ、為了系統調試的方便,很可能要求顯示中間處理的結果,因此我們在 FPGA 上掛接了一塊顯示調試模塊,調試時FPGA 可從SDRAM 中讀取中間的處理結果進行顯示。

Ⅳ、還有一種情況,某些情況下我們可能要求 DSP 和FPGA 之間直接進行圖像數據的傳輸,這也是我們必須考慮的范疇。

綜合上面的種種可能情況,考慮我們采用的 DSP 芯片同時支持FIFO 和SDRAM 芯片的無縫連接,我們設計了圖3 的數據傳輸方案:

首先,前端的采集模塊輸出的圖像數據是 8 位的,而對于我們采用的SDRAM 存儲芯片和DSP 處理芯片,數據總線都是64 位的。為了不造成資源的浪費,在FPGA 對圖像進行預處理的過程中,我們同時將8 位的圖像數據拼接成64 的數據輸出,這樣可充分利用系統的資源。

其次,在 FPGA 中經過一系列并行預處理的圖像數據,存儲于FPGA 內部開辟的FIFO中。FPGA 給出握手信號,通知DSP 可以開始由FIFO 向SDRAM 傳輸數據,數據的傳輸過程則完全由DSP 通過EDMA 傳輸方式來控制完成。當核心處理器DSP 完成當前操作的情況下,再從SDRAM 中讀入最新的數據進行處理,這可充分利用DSP 芯片豐富的外設資源。

同時,由圖 3 的數據流圖我們發現數據在由FPGA 向SDRAM 傳輸的過程中,相對于DSP 來說,FPGA 中開辟的用來存儲數據的FIFO 模塊和外部主存儲器SDRAM 模塊是掛接于DSP 上的相同的地址總線和數據總線上的,在這種源設備和目的設備掛接于相同外部總線上的傳輸形式下,我們采用的DSP 芯片支持一種優化的EDMA 傳輸模式-PDT 傳輸,它優化了數據的傳輸過程,使得DSP 的EDMA 傳輸模式可在數據不經過DSP 內的緩存區的情況下,直接由源設備FIFO 傳輸到目的設備SDRAM 中,從而可在一個周期內完成數據的傳輸。相比于傳統的傳輸模式,先由FPGA 傳輸到DSP 內部的緩存區,再由DSP 寫入到SDRAM 中,PDT 傳輸模式基本上可縮短一半的數據傳輸時間,對于像圖像這樣的大容量數據傳輸來說,是具有非常大的意義的。

評論