可用于汽車娛樂和導航系統的3G-SDI解決方案

SDI 是串行數字接口,被用來傳送無壓縮的數字視頻信號。在上世紀80年代,SDI得到了快速發展并對其標準作出了定義。3G-SDI中的3G是指SDI信號的數據傳輸率為3Gbit每秒。由于HDTV可以支持每秒30幀的逐行掃描1920×1080的分辨率格式,而3G能夠支持比HD視頻信號最高幀掃描頻率高一倍的頻率,即3G可以支持每秒60幀的HD信號,這在觀看動態視頻時的差別是很大的。

本文引用地址:http://www.104case.com/article/197732.htmSMPTE424M定義了3G-SDI的物理層及這類電信號的特征性能。傳送的信號應該有800mV的電壓擺幅,上升和下降時間必須小于135ps,允許有一些過沖的存在,但不可以超過10%,即 80mV。在SMPTERP184中規定了時鐘抖動和調整抖動的定義,它們需要的抖動參數分別小于2UI和0.2UI,調整抖動參數實際上要求是 0.3UI,但是SMPTE強烈推薦使用0.2UI的參數要求,因此本文將使用0.2UI的參數要求。接收器中,在10Hz到297MHz的頻帶內,輸入抖動容限,從2UI到0.2UI。發送器的輸出與接收器的輸入都應該被優化以保證回波損耗。

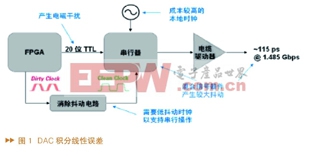

在發送器中,大部分抖動來自于串行器,電纜驅動器也會增加一些抖動。圖1所示為目前正在使用的發送器的典型框圖,它可以工作到HD、SDI,但是它不支持3G-SDI。由于20位的數字視頻總線已經在HD中制造了EMI問題,而在3G中該時鐘頻率加倍,因此EMI問題在3G中將更加嚴重。此外,PCB的布線也不是一項簡單的工作,工程師將要面對在 148.5MHz工作下的20條印制線。FPGA產生的時鐘信號也包含很多抖動,因此這些時鐘是不適合直接用于串行器的,由于會增加串行器的輸出抖動,從而需要加入抖動消除電路或Genlock電路以消除抖動。此外,有一些串行器也要求一個干凈的本地時鐘,這些抖動和本地時鐘不僅增加了系統成本,也占用了 PCB的面積。最后,串行器是一個模擬信號器件,包含了數字處理單元以及模擬串行單元,因此產生低抖動的模擬數字信號很困難。以HD信號為例,最小可以實現的輸出抖動大約為115ps或0.17UI,因此如果要支持3G,必須要采用全新的結構。

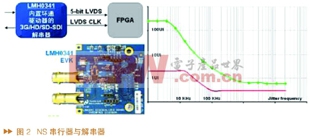

NS的SDI串行器和解串器產品創新的結構為SDI-3G提供了低輻射、低成本、低抖動和高性能的解決方案,在FPGA和串行器或解串器之間采用了 LVDS技術,從而去除了TTL連接。由于LVDS具有非常低的EMI輻射和功率損耗,因此非常適合應用在手持產品中。另外,PCB的印刷線也從20根減少到10根,使得PCB的設計更加容易。由于芯片內部設計了高性能PLL鎖相環,不再需要外置本地時鐘及抖動消除電路,因此系統成本得到了明顯的降低,同時節約了電路板的面積。因為FPGA已經存在于系統中,不需要額外的費用,因此大部分數字信號處理工作可以由FPGA完成,如CRC及行號插入、光柵、 ANC和EDH插入等。事實上,由于最困難的串行工作現在已經由串行器來完成了,因此可以降低FPGA的等級。這種串行由于采用了優秀的模擬技術工藝和高精度的鎖相環,因此可以提高解串器的抖動容限,最低可以達到0.6UI。和串行器類似,我們在解串器中也可以集成類似的環路,它可以簡化設計和減小空間,所以這樣的解串器不需要本地的時鐘,它是一個微小空間的7×7毫米的LLP封裝,如圖2所示。

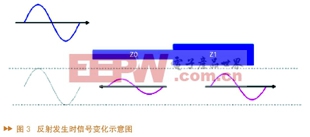

當信號從一種介質傳送到另外一種新的介質時,一部分信號將會被反射,剩余的信號將穿過這個介質。聲光和電磁波都有類似的特性,這是因為當介質改變時介質的密度和特性會發生變化。在傳輸線的原理中,印制電路線的寬度和其特性阻抗成正比,所以信號在兩個不同阻抗的印制電路線間傳輸時反射就會發生,反射的發生會減小信號的能量,影響接收器的處理,同時信噪比也會減小。另外當信號朝著源的方向被反射回來時,它會和原始的信號相混合疊加,降低信號的完整性,如圖3所示。

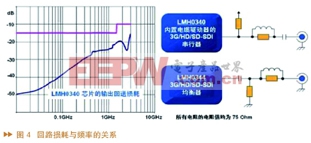

回送損耗可以用來衡量兩種阻抗匹配的優劣。通常的BNC連接器、電路板走線、電纜驅動器,輸出阻抗或均衡器的阻抗都各不相同,所以在實際的應用中需要考慮SMPTE嚴格的回送損耗指標要求。回路損耗是和頻率相關的參數,當頻率升高時,寄生電容和電感變得更加的明顯,它會使回路損耗變差。NS的SDI 系列產品都有很好的輸入輸出回路損耗特性,只需要使用一個簡單的小網絡就可以實現和BNC連接器的匹配。最普通的網絡可以通過將一個小小的電感和一個 75Ω的電阻并聯來實現,這個匹配網絡在直流特性時應該看起來象一個短路線,允許由終端電阻來提供傳輸線阻抗;在很高的工作頻率條件下寄生電容的阻抗值將會占主要的部分,這時回路損耗補償網絡可以提供75Ω的阻抗作為終端電阻,如圖4。

評論