DDR SDRAM在高速數(shù)據(jù)采集系統(tǒng)中的應(yīng)用

|

機(jī)的動(dòng)作,通過(guò)翻譯控制信號(hào)控制內(nèi)部狀態(tài)機(jī)產(chǎn)生控制DDR的正確時(shí)序信號(hào),這一部分是主控制模塊的關(guān)鍵和難點(diǎn),能否正確控制DDR的操作完全集中在此模塊

(2)外部刷新模塊是輔助主狀態(tài)機(jī)模塊控制DDR處于空閑狀態(tài)時(shí)的定時(shí)刷新

(3)地址發(fā)生模塊的作用是根據(jù)所接收由主控狀態(tài)機(jī)發(fā)送來(lái)的內(nèi)部命令產(chǎn)生所對(duì)應(yīng)的地址,然后將命令和對(duì)應(yīng)的地址同步發(fā)送給命令發(fā)送模塊

(4)命令發(fā)生模塊是與DDR芯片的接口部分,其將從地址模塊發(fā)送來(lái)的具體命令解釋成DDR所需的命令信號(hào)和控制信號(hào)![]()

以及所需的地址信號(hào)

以及所需的地址信號(hào)![]() (AO~A12,BA0,BAl)

(AO~A12,BA0,BAl)

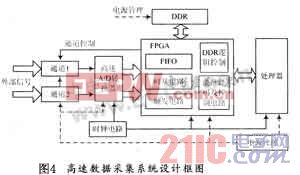

4 高速數(shù)據(jù)采集系統(tǒng)的結(jié)構(gòu)設(shè)計(jì)

為了能更清楚地了解DDR在高速數(shù)據(jù)采集系統(tǒng)中的應(yīng)用,這里將對(duì)基于CPCI總線的高速數(shù)據(jù)采集系統(tǒng)結(jié)構(gòu)進(jìn)行描述 高速數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)框圖如圖3所示

高速數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)框圖如圖3所示

|

外部信號(hào)首先經(jīng)過(guò)模擬通道的調(diào)理達(dá)到A/D芯片的輸入要求,再通過(guò)A/D芯片將模擬信號(hào)轉(zhuǎn)換成數(shù)字信號(hào)送人FPGA處理 當(dāng)處理器發(fā)出寫(xiě)命令時(shí),把數(shù)字信號(hào)在FIFO內(nèi)部進(jìn)行緩存再送入DDR進(jìn)行存儲(chǔ).如果A/D的采樣速率為200 MSa/s,則可以使用133 MHz時(shí)鐘速率的DDR芯片即可達(dá)到要求

當(dāng)處理器發(fā)出寫(xiě)命令時(shí),把數(shù)字信號(hào)在FIFO內(nèi)部進(jìn)行緩存再送入DDR進(jìn)行存儲(chǔ).如果A/D的采樣速率為200 MSa/s,則可以使用133 MHz時(shí)鐘速率的DDR芯片即可達(dá)到要求 但是在內(nèi)部進(jìn)行緩存時(shí)存在一個(gè)問(wèn)題,就是寫(xiě)入F1F()的時(shí)鐘速率大于讀取FIFO的時(shí)鐘速率,這樣就會(huì)導(dǎo)致從A/D采樣過(guò)來(lái)的信號(hào)不能完整地存儲(chǔ)

但是在內(nèi)部進(jìn)行緩存時(shí)存在一個(gè)問(wèn)題,就是寫(xiě)入F1F()的時(shí)鐘速率大于讀取FIFO的時(shí)鐘速率,這樣就會(huì)導(dǎo)致從A/D采樣過(guò)來(lái)的信號(hào)不能完整地存儲(chǔ)

在這種情況下通常采用數(shù)據(jù)分流的方式進(jìn)行解決,即把采人FPGA的200 MHz的數(shù)據(jù)流分成2路100 M的數(shù)據(jù)流,分別存入相應(yīng)的FIFO內(nèi)再以133 MHz的時(shí)鐘速率讀出送DDR進(jìn)行存儲(chǔ),這樣就可以對(duì)信號(hào)進(jìn)行完整的存儲(chǔ) 當(dāng)然存儲(chǔ)過(guò)程還要通過(guò)DDR的控制模塊和FPGA內(nèi)部自帶的1P核的配合才能夠完成

當(dāng)然存儲(chǔ)過(guò)程還要通過(guò)DDR的控制模塊和FPGA內(nèi)部自帶的1P核的配合才能夠完成 同理,當(dāng)處理器發(fā)出瀆命令時(shí),在DDR控制模塊的控制下將DDR內(nèi)部數(shù)據(jù)讀回FPGA內(nèi)部,再次通過(guò)FIFO進(jìn)行緩存

同理,當(dāng)處理器發(fā)出瀆命令時(shí),在DDR控制模塊的控制下將DDR內(nèi)部數(shù)據(jù)讀回FPGA內(nèi)部,再次通過(guò)FIFO進(jìn)行緩存 通常采用40 M的時(shí)鐘速率將數(shù)據(jù)送回處理器處理,從DDR寫(xiě)回FPGA的數(shù)據(jù)流時(shí)鐘速率為133 M,而從FIFO讀}IJ數(shù)據(jù)的時(shí)鐘速率為40 M;同樣存在著寫(xiě)入FIFO的時(shí)鐘速率大于讀取的時(shí)鐘速率的現(xiàn)象,但足這里不仔在數(shù)據(jù)丟火的問(wèn)題,岡為前端的分流處理已經(jīng)保證了數(shù)據(jù)的完整性

通常采用40 M的時(shí)鐘速率將數(shù)據(jù)送回處理器處理,從DDR寫(xiě)回FPGA的數(shù)據(jù)流時(shí)鐘速率為133 M,而從FIFO讀}IJ數(shù)據(jù)的時(shí)鐘速率為40 M;同樣存在著寫(xiě)入FIFO的時(shí)鐘速率大于讀取的時(shí)鐘速率的現(xiàn)象,但足這里不仔在數(shù)據(jù)丟火的問(wèn)題,岡為前端的分流處理已經(jīng)保證了數(shù)據(jù)的完整性 這里只需對(duì)FIFO及DDR進(jìn)行控制,即對(duì)FIFO的使用率做一個(gè)控制,當(dāng)FIFO的使用率大于某一值時(shí),停止從DDR中讀取數(shù)據(jù);當(dāng)小于這個(gè)值時(shí),繼續(xù)從DDR中讀取數(shù)據(jù)

這里只需對(duì)FIFO及DDR進(jìn)行控制,即對(duì)FIFO的使用率做一個(gè)控制,當(dāng)FIFO的使用率大于某一值時(shí),停止從DDR中讀取數(shù)據(jù);當(dāng)小于這個(gè)值時(shí),繼續(xù)從DDR中讀取數(shù)據(jù) 這樣就有足夠的數(shù)據(jù)可進(jìn)行分析處理,從而重現(xiàn)信號(hào)特征

這樣就有足夠的數(shù)據(jù)可進(jìn)行分析處理,從而重現(xiàn)信號(hào)特征

5 結(jié) 語(yǔ)

DDR在高速數(shù)據(jù)采集系統(tǒng)中的應(yīng)用有很大的實(shí)際意義,他提高了系統(tǒng)的可靠性和數(shù)據(jù)的存儲(chǔ)深度,在一定程度上有效地減小了電路設(shè)計(jì)的尺寸 DDR已經(jīng)被應(yīng)用于視頻采集、內(nèi)存設(shè)計(jì)等多個(gè)領(lǐng)域

DDR已經(jīng)被應(yīng)用于視頻采集、內(nèi)存設(shè)計(jì)等多個(gè)領(lǐng)域 其關(guān)鍵技術(shù)是DDR時(shí)序控制模塊的設(shè)計(jì)

其關(guān)鍵技術(shù)是DDR時(shí)序控制模塊的設(shè)計(jì)

評(píng)論