5 Gsps高速數據采集系統的設計與實現

從圖3(a)中的數據可以看出,各個通道均以約定的格式輸出,說明ADC與FPGA之間數據接口已經準確連通。圖3(b),輸入正弦信號時用BUS PLOT工具將抓取到的數據實時畫圖,得到的波形平滑,計算其信噪比為42.9 dB,由式(2)計算得到ADC的有效位數為6.6 bit。實測表明,AD9520輸出的2.5 GHz時鐘以及EV8AQ160均具有較高的性能,整體指標達到設計要求。

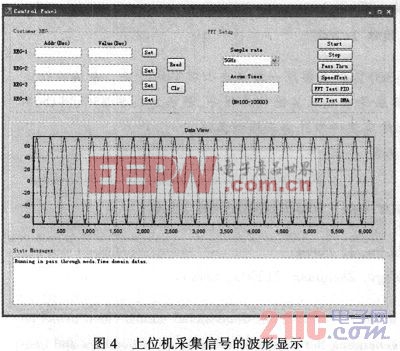

2)上位機數據結果顯示

用戶應用窗口程序的設計是在Visual Studio 2008環境下進行的,內部通過調用WinDriver提供的API函數及已編寫的驅動函數,可以打開、查看、配置和關閉該PCI Express硬件設備。將系統配置為5 Gsps采樣率的工作模式,用TeeChart畫出實時采集到的波形,如圖4所示,表明系統實現了數據的實時采集存儲功能。本文引用地址:http://www.104case.com/article/193738.htm

3 結束語

采用FPGA作為數據采集系統的控制核心,使用FPGA內部資源或者外部DDR3實現數據的緩沖存儲,充分利用系統資源,便于調試和修改。實現了5 Gsps實時采樣率、8 bits采樣精度的高速實時數據采集系統。在完成電路的軟件和硬件設計以后,通過對ADC和時鐘進行測試以及上位機控制界面采集信號的波形顯示,結果表明該系統可以穩定地工作,滿足設計要求。

評論