5 Gsps高速數據采集系統的設計與實現

摘要:以某高速實時頻譜儀為應用背景,論述了5 Gsps采樣率的高速數據采集系統的構成和設計要點,著重分析了采集系統的關鍵部分高速ADC(analog to digital,模數轉換器)的設計、系統采樣時鐘設計、模數混合信號完整性設計、電磁兼容性設計和基于總線和接口標準(PCI Express)的數據傳輸和處理軟件設計。在實現了系統硬件的基礎上,采用Xilinx公司ISE軟件的在線邏輯分析儀(ChipScope Pro)測試了ADC和采樣時鐘的性能,實測表明整體指標達到設計要求。給出上位機對采集數據進行處理的結果,表明系統實現了數據的實時采集存儲功能。

關鍵詞:高速數據采集;高速ADC;FPGA;PCI Express

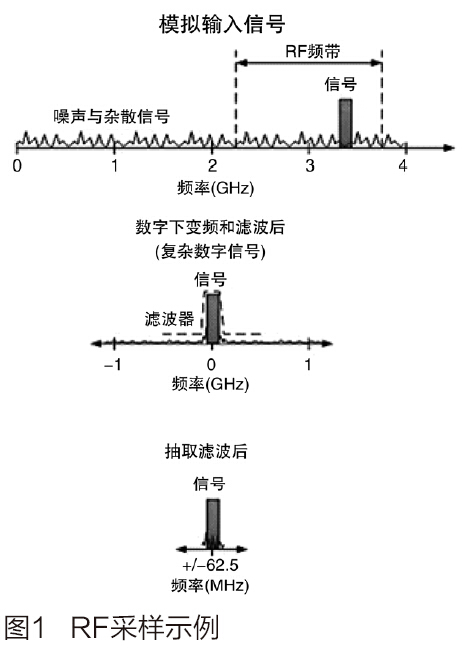

高速實時頻譜儀是對實時采集的數據進行頻譜分析,要達到這樣的目的,對數據采集系統的采樣精度、采樣率和存儲量等指標提出了更高的要求。而在高速數據采集系統中,ADC在很大程度上決定了系統的整體性能,而它們的性能又受到時鐘質量的影響。為滿足系統對高速ADC采樣精度、采樣率的要求,本設計中提出一種新的解決方案,采用型號為EV8AQ160的高速ADC對數據進行采樣;考慮到ADC對高質量、低抖動、低相位噪聲的采樣時鐘的要求,采用AD9520為5 Gsps數據采集系統提供采樣時鐘。為保證系統的穩定性,對模數混合信號完整性和電磁兼容性進行了分析。對ADC和時鐘性能進行測試,并給出上位機數據顯示結果,實測表明該系統實現了數據的高速采集、存儲和實時后處理。

1 系統的構成

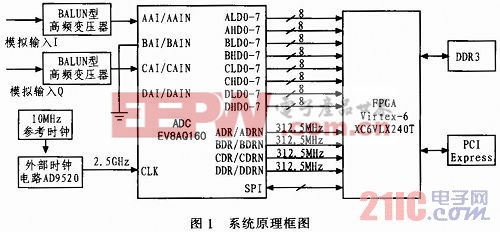

高速數據采集系統主要包括模擬信號調理電路、高速ADC、高速時鐘電路、大容量數據緩存、系統時序及控制邏輯電路和計算機接口電路等。圖1所示為5 Gsps高速數據采集系統的原理框圖。所用ADC型號為EV8AQ160,8 bit采樣精度,內部集成4路ADC,最高采樣率達5 Gsps,可以工作在多種模式下。通過對ADC工作模式進行配置,ADC既可以工作在采樣率為5 Gsps的單通道模式,也可以工作在采樣率為2.5 Gsps的雙通道模式。模擬輸入信號經過BALUN型高頻變壓器完成單端信號到差分信號的轉換,ADC對差分信號進行采樣,然后把數據送入FPGA,FPGA將接收到的數據進行預處理后存儲到第三代雙倍速率同步動態隨機存儲器(DDR3)中,需要對采集的數據進行后續處理時,將數據從DDR3中取出,并通過PCI Express傳送給上位機,上位機對數據進行處理后顯示。整個硬件系統僅采用一片FPGA來處理,并作為主控芯片對整個系統進行通信和控制,大大提高了系統的運行速度。本設計采用Xilinx公司Virrex-6系列FPGA,型號為XC6VLX240T-1156C。

2 系統的設計與實現

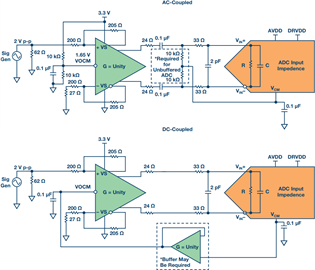

2.1 高速ADC設計及其完整性分析

高速ADC芯片EV8AQ160在片內集成了4路獨立的ADC,每個通道具有1.25Gsps的采樣率,可以工作在3種模式下,最高采樣率可達5Gsps。要求2.5 GHz差分對稱時鐘輸入,可進行ADC主復位。EV8AQ160內部集成了1:1和1:2的數據多路分離器(DMUX)和LVDS輸出緩沖器,可以降低輸出數據率,方便與多種類型的高速FPGA直接相連,實現高速率的數據存儲和處理。為了補償由于器件參數離散和傳輸路徑差異所造成的采樣數據誤差,該ADC具有針對每路ADC數據的積分非線性(INL)、增益(Gain)、偏置(Offset)、相位(Phase)的控制和校正。EV8AQ160提供測試功能,具有兩種測試方式,方便用戶根據自己的習慣對ADC是否正常工作進行測試。

評論