基于FPGA的全數字鎖相環的設計

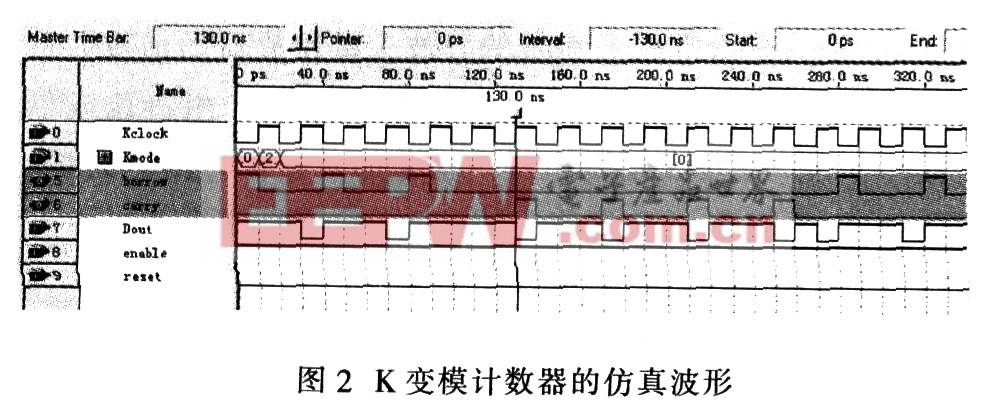

上述代碼經過在Quartus II上編譯仿真后其波形如圖2所示。本文引用地址:http://www.104case.com/article/192143.htm

設計中適當選取K值特別的重要。如果K值偏大,這樣計數器對少量噪聲干擾不可能計滿,就不會有進位或者借位脈沖,有利于抑制隨機噪聲;但就會使捕捉帶減小,導致環路進入鎖定的時間變長;如果K值偏小,可使環路盡快進入鎖定狀態,但會減弱對噪聲的抑制能力,導致環路頻繁的產生進位或借位脈沖,造成整個系統不穩定,產生相位抖動問題。所以要適當選取K值。

3.3 數控振蕩器

數控振蕩器采用的是脈沖加減電路。時鐘為2Nfc。當沒有進位/借位信號時,其輸出對外部時鐘進行二分頻;當有進位信號carry輸入時,則在原信號中插入半個脈沖,以提高原有信號的頻率;當有借位信號borrow輸入時,則減去半個脈沖,以降低原有信號的頻率。

3.4 可變分頻器

可變分頻器實際上就是一個除N計數器,是把脈沖加減電路的輸出信號再做N分頻,通過不斷調整N值的大小,使分頻器的輸出信號能與輸入信號的相位保持同步,以達到鎖相環的鎖定。

由鎖相環的整個工作過程可知,全數字鎖相環經過一些特定改良后,可在某些情況下作為滿足一定頻率要求的信號發生器使用。

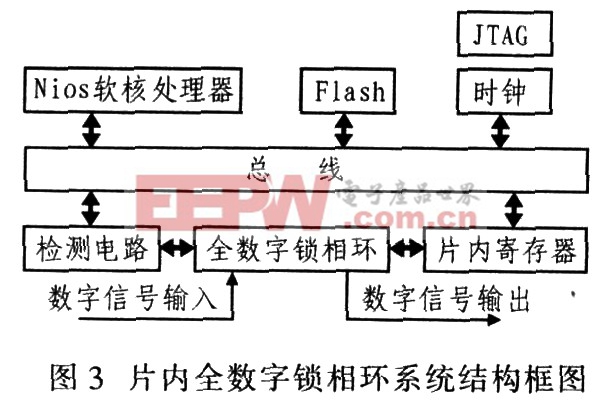

4 FPGA片內系統結構

為了平衡系統的穩定性和捕獲帶寬之間的矛盾,就要找到一個最佳的K值,使系統在最大可能消除干擾的前提下,捕捉帶達到最大,捕獲時間最短,其整個過程由CPU來控制。CPU的選擇主要有2種方案:①FPGA片內實現CPU;②與片外系統共用CPU。這里主要介紹第一種。

對于片內CPU,這里采用Ahera公司推出的NiosⅡ嵌入式軟核處理器予以實現。在系統中,片內寄存器,全數字鎖相環以及檢測電路均作為外設嵌入到FPGA芯片中。片內寄存器,全數字鎖相環,檢測電路通過系統總線相連接,受到片內的NiosⅡ軟核處理器的控制,使得全數字鎖相環中的數字環路濾波器部分在工作中的參數得到優化。此種結構使得NiosⅡ處理器和全數字鎖相環2部分集成在一塊FPGA器件中,大大提高了系統的穩定性和可靠性。罔3給出片內全數字鎖相環系統結構框圖。

5 試驗仿真結果分析

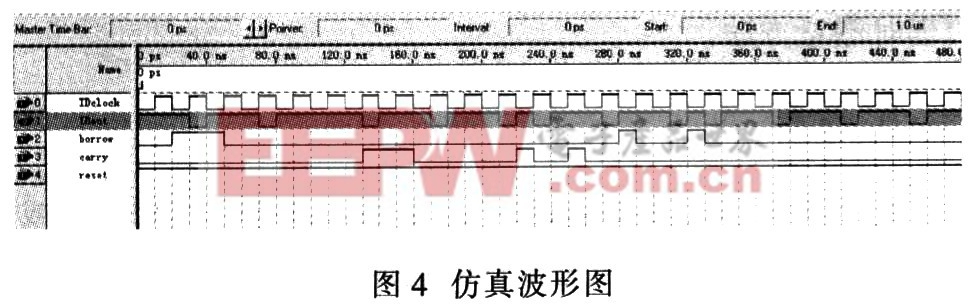

整個系統經過軟硬件調試后,就對該鎖相環進行測試和驗證,采用Quartus II軟件中集成的仿真器進行仿真。圖4給出仿真波形。

可見,在有進位/借位信號輸出時,波形中自動加入/減去半個脈沖,經過幾次調整后系統達到鎖定狀態。

6 結語

通過在單片FPGA中實現智能全數字鎖相環,NiosⅡ嵌入式處理器隨時檢測鎖相環的狀態,適時調整鎖相環的參數,從而能縮短鎖相環鎖定時間,提高效率;并逐漸改進其輸出頻率的抖動特性。解決了鎖定時間與相位抖動之間的矛盾,提高了信息的傳輸效率和質量。全數字鎖相環在數字通信,數字信號處理,電力系統自動化等眾多領域有著極為廣泛的應用,隨著片內數字鎖相環系統研究的不斷深入與發展,其性能會不斷提高,其意義重大,前景廣闊。

濾波器相關文章:濾波器原理

fpga相關文章:fpga是什么

濾波器相關文章:濾波器原理

分頻器相關文章:分頻器原理 塵埃粒子計數器相關文章:塵埃粒子計數器原理 鑒相器相關文章:鑒相器原理 數字濾波器相關文章:數字濾波器原理 鎖相環相關文章:鎖相環原理 鎖相放大器相關文章:鎖相放大器原理

評論