基于PLD的納秒級脈沖發(fā)生器

本設(shè)計選用的外部計數(shù)時鐘頻率為100 MHz,因此所產(chǎn)生脈沖的周期最小是10 ns,脈寬調(diào)節(jié)最小為5 ns,調(diào)節(jié)步長為5 ns。該脈沖發(fā)生器可以實現(xiàn)多路輸出,脈沖輸出共有9路,其中1路可以實現(xiàn)單脈沖輸出,其余8路可以輸出不同脈寬的納秒級脈沖。若要提高脈沖發(fā)生器的精度,應(yīng)提高計數(shù)時鐘的頻率。同時選用速度等級更高的PLD。若要增加脈沖周期及脈寬的可調(diào)范圍,則應(yīng)選用容量更大的PLD。

本文引用地址:http://www.104case.com/article/192124.htm2 仿真驗證

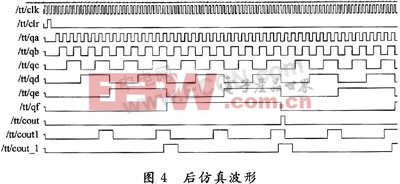

仿真是驗證設(shè)計的一個重要環(huán)節(jié),如果仿真沒有通過,設(shè)計就必須重來,以便硬件調(diào)試的勝利通過。在ISE中,建立仿真文件并調(diào)用ModelSim 6.0對設(shè)計進行行為仿真。在第2個脈沖到來時進行計數(shù)器置零,開始計數(shù),對每個輸出端口的波形都進行仿真測試。從仿真波形中可以預(yù)測出,可編程器件成功地對脈沖進行控制,然后分頻輸出,達到預(yù)定的要求。

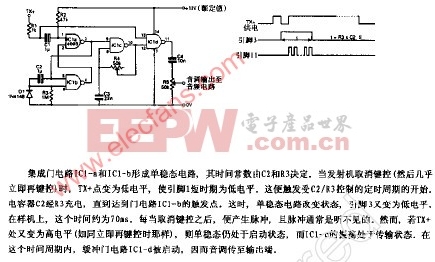

行為仿真只是對VHDL語言進行邏輯綜合后仿真,布局布線后仿真則是在具體器件和硬件資源分配后,利用從布局布線中提取的一些信息,其中包括了目標器件及互連線的時延、電阻、電容等信息,并考慮走線之間的相互影響后產(chǎn)生的仿真波形。圖4是布局布線后仿真圖,可以看到在CLR信號有效開始,輸出端經(jīng)過4個周期的延遲后才響應(yīng)到有效的復(fù)位信號,這個說明器件延時加上互連線延時為4個周期,但是這并不影響設(shè)計輸出脈沖的質(zhì)量,在其他電子設(shè)計中卻要考慮到這個延遲。

|

3 試驗結(jié)果

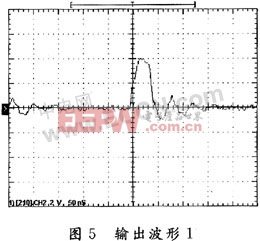

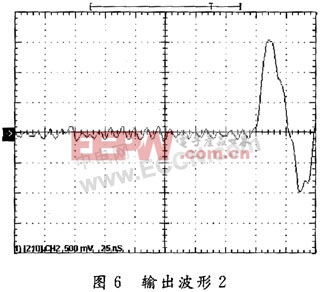

做好電路版,調(diào)試程序成功后,用型號為TektronixTDS210示波器測出兩個端口的輸出波形如圖5和圖6所示。圖5中波形幅度為3.98 V,峰峰值為4.98 V,脈沖寬度為37.8 ns,上升沿為16.7 ns;圖6波形幅度為1.53 V,峰峰值為2.51 V,脈沖寬度為19.8 ns,上升沿為9.7 ns。在示波器中顯示,得到納秒脈沖信號非常穩(wěn)定,可以作為一個穩(wěn)定的納秒信號源。每個脈沖過后都有一個小的負脈沖,并且上升沿和下降沿并沒有像仿真時短,主要原因是:一是仿真在一個相對理想的條件下進行的,對器件資源在電路中的實際體積忽略;二是芯片的微加工制造工藝不精確,寄生電容電阻的大小沒有精確計算,可以在輸出端加電容接地減小過脈沖。

|

相關(guān)推薦

技術(shù)專區(qū) |

評論