動(dòng)態(tài)重構(gòu)兩種模式的分析與對(duì)比

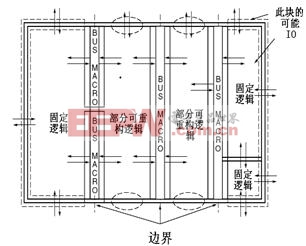

圖2 具有兩個(gè)可重構(gòu)模塊的設(shè)計(jì)布局圖

4、總線宏的通訊

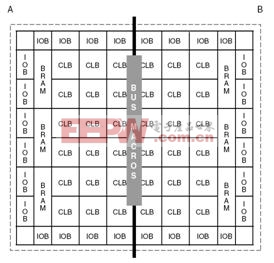

為了促進(jìn)可重構(gòu)模塊之間的通信,需要保證穿過(guò)可重構(gòu)模塊邊界的布線資源是完全固定而且必須是靜態(tài)的,這就需要一種特殊的總線宏。如圖3就是所需的這種總線宏。

其中,左邊的A是一個(gè)模塊,右邊的B是另一個(gè)模塊,A或者B是可重構(gòu)模塊,或者AB全是可重構(gòu)模塊。A和B中間的總線宏,就是支持AB之間通信的特殊總線宏。它保證AB間布線資源的不變性。也就是說(shuō)當(dāng)一個(gè)模塊進(jìn)行重構(gòu)時(shí)模塊內(nèi)部信號(hào)用到的布線資源不能改變。如圖3,總線宏是兩個(gè)模塊間的一個(gè)固定的布線橋。它是一個(gè)事先已經(jīng)布線好的用來(lái)確定精確布線軌道的宏,并且在編輯改變的時(shí)候保持不變。對(duì)于每個(gè)不同的設(shè)計(jì)應(yīng)用來(lái)說(shuō),它是一個(gè)絕對(duì)固定不變的總線宏。

圖3 總線宏

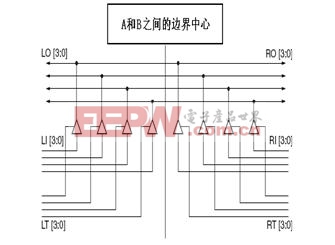

目前使用的總線宏由八個(gè)三態(tài)緩沖器組成如圖4。總線宏允許信息雙向傳遞,一個(gè)比特的信息使用一個(gè)三態(tài)緩沖器的長(zhǎng)線。Virtex器件的每一行支持一個(gè)總線宏的四個(gè)固定的通信。總線宏的信息通訊是雙向的,既可以從左到右又可以從右到左。但是對(duì)于這個(gè)設(shè)計(jì)來(lái)說(shuō),一旦信息通信方向確定以后就不能再改變。

圖4 總線宏的物理執(zhí)行

5、基于差異的部分可重構(gòu)

基于差異的部分可重構(gòu)比較重構(gòu)前后的電路差別,產(chǎn)生一個(gè)只包含重構(gòu)前后設(shè)計(jì)差別的比特流。可以使用兩種方法來(lái)改變?cè)O(shè)計(jì)、產(chǎn)生重構(gòu)前后的差別,分別是前端改變(HDL描述)和后端改變(NCD文件)。使用前端改變,設(shè)計(jì)必須重新綜合,創(chuàng)建新的NCD文件。后端改變只需直接修改NCD文件,不必重新綜合,可通過(guò)FPGA Editor工具修改NCD文件。

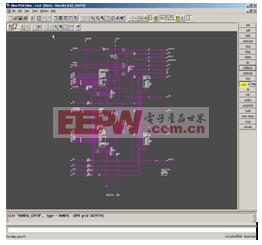

在FPGA Editor中可以進(jìn)行三種方式的修改:改變I/O標(biāo)準(zhǔn)、BRAM內(nèi)容、LUT設(shè)計(jì)。其中可以選擇的最小邏輯元素是slice。首先打開(kāi)NCD文件,看到邏輯塊后找到可選擇的最小邏輯元素slice,打開(kāi)slice的結(jié)構(gòu)圖窗口,可以分別將重構(gòu)前的I/O標(biāo)準(zhǔn)、BRAM內(nèi)容、LUT設(shè)計(jì)修改為重構(gòu)后的形式,如圖5所示。

圖5 改變LUT設(shè)計(jì)

以上三種修改都符合有效的重構(gòu)流程。除了這三種方式還有其他的修改方式,比如:顛倒極性、振蕩器的初始化和重新設(shè)置值、上拉、下拉外部管腳或者RAM寫方式。所有這些特性都能夠在實(shí)際的slice、RAM邏輯塊或IOB中修改。但是,最好不要進(jìn)行任何有可能影響布線或者產(chǎn)生內(nèi)部連接沖突的修改行為。

實(shí)現(xiàn)上述修改后,使用BitGen就可產(chǎn)生可下載的差異比特文件。可重構(gòu)前后開(kāi)關(guān)配置的改變非常迅速,比重新配置整個(gè)電路要快很多,就像差異比特流比整個(gè)電路的比特流小很多一樣,所以能夠迅速而簡(jiǎn)單的下載到電路中。

6、結(jié)論

當(dāng)電路只需要修改比較少的內(nèi)容時(shí),往往選擇基于差異的部分可重構(gòu)。差異比特流比整個(gè)電路的比特流小很多,所以能夠迅速下載到電路中。

但是如果電路功能比較復(fù)雜則差異文件會(huì)非常龐大,部分動(dòng)態(tài)重構(gòu)的優(yōu)勢(shì)并不十分明顯。所以基于差異的部分可重構(gòu)只適用于功能簡(jiǎn)單的電路,對(duì)于功能復(fù)雜的電路需要使用基于模塊的部分可重構(gòu)。

綜上所述,基于差異和基于模塊的部分動(dòng)態(tài)重構(gòu)都可以大大節(jié)省系統(tǒng)的硬件資源,加快文件的下載速度,提高資源利用率,相信會(huì)有廣闊的研究和應(yīng)用前景。

評(píng)論