基于FPGA的電子琴動態錄音與回放系統的設計

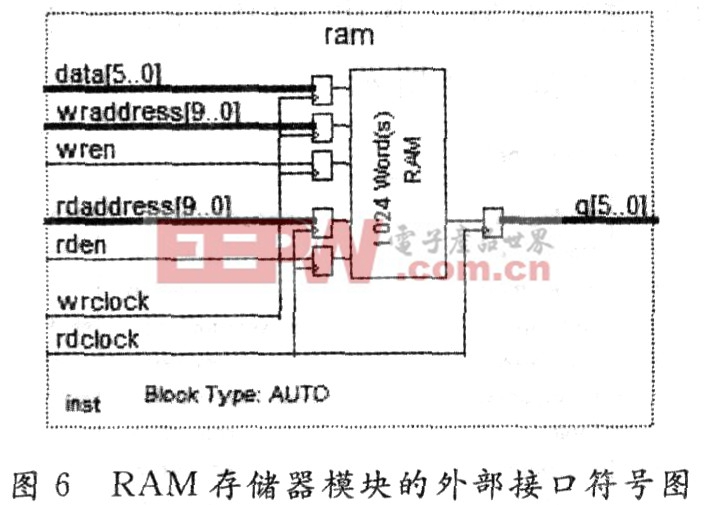

設計一個雙端口的存儲深度為1 024、存儲寬度為6位的隨機存儲器RAM,用來存儲彈奏的樂曲,并可播放出來。生成的RAM單元如圖6所示。data[5..O]端口為彈奏電子琴時由發聲控制模塊產生的音符數據。本文引用地址:http://www.104case.com/article/192067.htm

當系統處于“錄音/回放模式”的“錄音”狀態時,將當前所彈奏的音符進行轉換,輸出作為RAM的存儲數據“DATA”。wraddress[9..O]代表十位寬度的寫地址端口,rdaddress[9..0]代表十位寬度的讀地址端口。wrclock為RAM寫入時鐘,rdclock為RAM讀出時鐘。Q[5..0]為從RAM中讀出所存放數據,即data。從圖6可以看出,此雙口RAM具有獨立的讀寫時鐘和讀寫使能。選擇這樣的RAM的目的是為了以一個固定頻率wrclock(本設計取4 Hz)的時鐘對RAM進行寫操作,即以一個固定的采樣頻率對所彈奏的樂曲進行采樣存儲;另一方面以節奏控制部分輸出的時鐘rdclock作為RAM的讀時鐘信號,使得回放過程可以以不同的節奏將儲存的樂曲播放出來。這是其新穎之處,使電子琴在回放過程中更加靈活多變,功能更多。

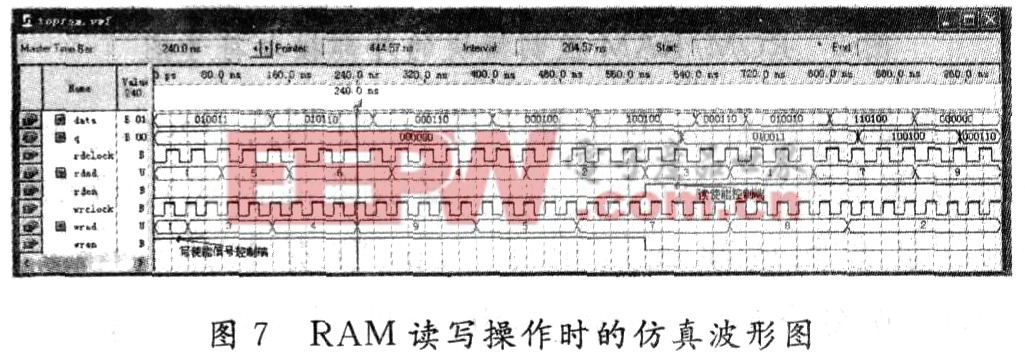

其仿真波形圖如圖7所示。從仿真圖上可以看出,RAM存儲器在寫使能信號和讀使能信號控制作用下依次寫入數據信號,并按寫入地址先后次序再準確地讀出來,實現了錄音和回放的功能要求。

本設計采用杭州康芯電子有限公司開發的電子設計應用板(型號:KX―DVP3F)進行對系統的調試與功能驗證。利用QuartusⅡ6.O軟件生成.sol或者.pof編程文件,通過USB下載器將編程文件配置到CycloneⅡEP2C8Q208芯片中,經過數次的調試,多功能電子琴的全部技術指標和功能很好地符合設計要求,發聲準確,易操作,可視性強。

有限狀態機設計技術是實用數字系統中的重要組成部分,也是實現高效率高可靠邏輯控制的重要途徑。它具有類似CPU的高速運算和控制能力,程序層次分明,結構清晰,易讀易懂;在排錯、修改和模塊移植方面也有獨到之處。

評論